全新UltraScale+ FPGA、SoC与 3D IC应用涵盖LTE-A和初期5G无线、TB级有线通讯、车用先进驾驶辅助系统与工业物联网领域

|

| /news/2015/02/24/1548478650S.jpg |

美商赛灵思(Xilinx)宣布其结合了全新内存、3D-on-3D和多重处理系统芯片(MPSoC)技术的16奈米UltraScale+系列 FPGA、3D IC和MPSoC组件。此外,为实现更高的效能和整合度,UltraScale+系列加入了全新的SmartConnect互连优化技术。这些组件让赛灵思的UltraScale 产品阵容丰富多元,现在除了横跨20奈米和16奈米制程的FPGA、SoC和3D IC组件外,更运用台积公司16FF+ FinFET 3D晶体管大幅提升功耗效能比。UltraScale+提供可比28奈米组件提供高出二至五倍的系统级功耗效能比,并有高效的系统整合度和智能化,以及高安全性和保密性。

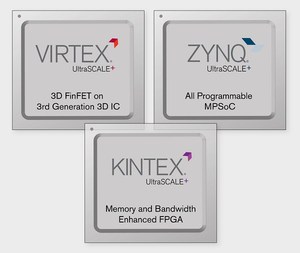

扩充后的全新Xilinx UltraScale+ FPGA产品阵容,包括赛灵思的Kintex UltraScale+ FPGA、 Virtex UltraScale+ FPGA 和3D IC系列组件,而Zynq UltraScale+系列则包含完全可编程的MPSoC组件。赛灵思藉由因应LTE-A和初期5G无线、TB级有线通讯、车用先进驾驶辅助系统(ADAS)和工业物联网等众多新一代应用的需求。

加强型内存可编程组件: UltraRAM技术可整合SRAM,并突破其中一项影响采用FPGA和SoC组件重大的系统效能和功耗瓶颈。这项全新的技术可为包括深层封包和视讯缓冲暂存等广泛应用建置高容量的芯片内建内存,并提供可预测的延迟率和效能。设计人员藉由整合非常接近联合处理引擎的大量嵌入式内存,即可获得更佳的系统功耗效能比和降低材料列表(BOM)成本。在许多配置中UltraRAM的容量,甚至可扩充到432MB。

SmartConnect技术:SmartConnect是一项针对FPGA设计的创新互连优化技术,透过智能型功能为整个系统的互连环境进行优化,可额外提升20%至30%的效能、更多面积和省电功能。UltraScale架构可藉由重新设计的布线、频率和逻辑架构突破芯片级的互连瓶颈,而SmartConnect技术则可运用互拓扑优化以因应特定设计的处理量和各种延迟率需求,同时可缩小互连逻辑组件占用的面积。

首项3D-on-3D技术:UltraScale+ 系列中的高阶产品同时运用了3D晶体管和赛灵思第三代3D IC的威力。如同FinFET技术可让平面晶体管功耗效能比呈非线性提升,3D IC可让单颗组件的系统整合度与功耗带宽比也呈现非线性的增长。

异质架构的多任务处理技术:全新的Zynq UltraScale+ MPSoC组件具备上述所有的FPGA技术,以及异质架构多重处理功能,因而「可让对的运算引擎处理合适的任务」而达到成效。这些全新组件提供的系统级功耗效能比是前代产品的五倍。而处理子系统的运算核心是64位的四核心ARM Cortex-A53处理器,拥有硬件虚碍化、非对称处理等功能,同时拥有完整的ARM TrustZone支持。

此外,处理子系统也包含一个可进行决定性作业的双核心ARM Cortex-R5 实时处理器,可确保系统的快速响应功能、高处理量和低延迟率,达到高安全性和可靠度。独立的安全单元更提供军事级的安全解决方案,例如安全开机、密钥和保管库管理,以及防窜改功能等,满足机器对机器通讯传输和工业物联网应用的标准需求。

为实现完整的图形加速视频压缩/解压缩功能,这一新的组件整合了ARM Mali-400MP专用图形处理器和H.265视频编译码器单元,同时还支持Displayport、 MIPI和HDMI。此外这些组件也有专属的平台和电源管理单元(PMU),可支持系统监控、系统管理和每个处理引擎的动态功耗闸控功能。

赛灵思执行副总裁暨可编程产品部门总经理Victor Peng表示:「赛灵思全新的16奈米Ultrascale+ 产品阵容可提供高出二至五倍的系统级功耗效能比、大幅提升的系统整合度和智能化功能,以及满足客户所需的高安全性和保密性。这些功能可让赛灵思大幅拓展更多市场。」

台积公司事业开发副总经理金平中博士表示:「台积公司与赛灵思长期合作的成果实现了16奈米FinFET产品系列。双方也明确地展现了拥有低功耗和高系统价值的优异芯片效能。」

赛灵思已向早期采用客户提供全线UltraScale+系列产品,首批组件投产和早期采用方案所需的设计工具预计于今年第二季推出,而首批组件也将于今年第四季出货。赛灵思于2月24~26日) 于德国纽伦堡登场的嵌入式电子与工业计算机应用展(Embedded World)中展示Zynq UltraScale+ MPSoC 技术。(编辑部陈复霞整理)