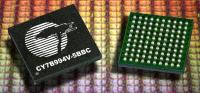

柏士半导体(Cypress Semiconductor)宣布,该公司推出以100针微间距的BGA(fBGA)封装的RoboClock II Programmable Skew Clock Buffer(可程序相差频率缓冲器)。柏士表示,该款产品所占的电路板空间不到TQFP版本产品的一半。fBGA封装的大小为11mmx11mm,并采用1mm的球状间距,加上RoboClock系列产品所特有的可程序性,可为网络、电信及大型储存应用产品的设计人员提供解决方案,使困难的电路板布局问题迎刃而解,进而降低产品研发成本并加快上市速度。

|

| 柏士推出新版可程序相差频率缓冲器RoboClock II |

柏士指出,RoboClock II系列产品扩充了原先RoboClock系列产品的功能,包括可程序相差(programmable skew)、零传播延迟(zero propagation delay)、50-50的运作周期(50-50 duty cycle),以及发射扩频信号的能力(spread-spectrum signal distribution)等。RoboClock II提供用户以1到6、8、10及12乘除频的能力,而原先的RoboClock只提供以1、2及4来乘除频的功能。RoboClock II具有18个输出,原先RoboClock仅有8个输出。RoboClock II fBGA封装版本,产品编号为CY7B994V-5BBC,运作速度可达185MHz。

柏士进一步指出,RoboClock II是第一套使用该公司新的3.3伏、双层金属、0.25微米BiCMOS制程所生产的产品。该公司完整测试所有RoboClock装置的重要相差规格,包括针对针的相差(pin-to-pin skew)、传播延迟(propagation delay),以及上升与下降时间(rise and fall time)等,保证产品稳定度及质量。