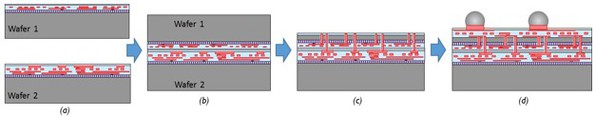

元件封装技术的创新步伐从未如今日这般高速并且有趣。以往的资讯经是由导线传送,而近年来,各种3D互连技术在封装中直接将构件相连接。随着3D互连密度呈指数级别的增长,线宽需要微缩至5μm或者更低(窄)。然而,目前的3D-SIC(3D堆叠IC)的互连技术并不能支持这样高的密度。如图1所示,通过并行的晶圆前段制程,并结合晶圆到晶圆(W2W)接合和极度晶圆薄化步骤,以及采用3D-SOC(3D系统晶片)整合技术方案,则可以让3D互连密度提升。

| 图1 : 针对3D-SOC应用的介电层晶圆至晶圆接合的整合方案。图左至图右分别为:上下晶圆对准、接合、薄化并进行下一步制程,例如TSV(矽穿孔)的後穿孔蚀刻、穿孔、导线和RDL(线路重布技术)。 |

|

在极度晶圆薄化制程的探索和开发过程中,文献[1]和[2]中针对5μm的最终矽(Si)厚度规格,对不同的薄化技术,如研磨、抛光和蚀刻进行了评估。为了比较这些薄化技术,文献中还定义了作为成功的薄化制程必须遵循的多项标准。首先,跨晶圆的最终Si厚度(FST)必须在一定的限度之内,这样才可以保证诸如一个稳定的後穿孔蚀刻制程,并且到达正确的导线层。

...

...

| 另一名雇主 |

限られたニュース |

文章閱讀限制 |

出版品優惠 |

| 一般訪客 |

10/ごとに 30 日間 |

5//ごとに 30 日間 |

付费下载 |

| VIP会员 |

无限制 |

20/ごとに 30 日間 |

付费下载 |