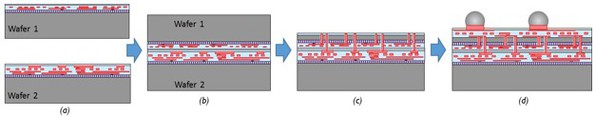

元件封裝技術的創新步伐從未如今日這般高速並且有趣。以往的資訊經是由導線傳送,而近年來,各種3D互連技術在封裝中直接將構件相連接。隨著3D互連密度呈指數級別的增長,線寬需要微縮至5μm或者更低(窄)。然而,目前的3D-SIC(3D堆疊IC)的互連技術並不能支持這樣高的密度。如圖1所示,通過並行的晶圓前段製程,並結合晶圓到晶圓(W2W)接合和極度晶圓薄化步驟,以及採用3D-SOC(3D系統晶片)整合技術方案,則可以讓3D互連密度提升。

| 圖1 : 針對3D-SOC應用的介電層晶圓至晶圓接合的整合方案。圖左至圖右分別為:上下晶圓對準、接合、薄化並進行下一步製程,例如TSV(矽穿孔)的後穿孔蝕刻、穿孔、導線和RDL(線路重佈技術)。 |

|

在極度晶圓薄化製程的探索和開發過程中,文獻[1]和[2]中針對5μm的最終矽(Si)厚度規格,對不同的薄化技術,如研磨、拋光和蝕刻進行了評估。為了比較這些薄化技術,文獻中還定義了作為成功的薄化製程必須遵循的多項標準。首先,跨晶圓的最終Si厚度(FST)必須在一定的限度之內,這樣才可以保證諸如一個穩定的後穿孔蝕刻製程,並且到達正確的導線層。

其次,薄化製程不應該對頂端的晶圓造成跨晶圓的Si損害,尤其是在晶圓邊緣,因其將直接損害完整晶圓堆疊的 良率。最後,晶圓表面奈米形狀(NT),形狀和平坦度必須在掌控之中,以便在超過N = 2的多晶圓疊層時可以確保隨後的W2W接合。為了讓我們能夠執行這些具有挑戰性的標準,所使用的量測系統必須可以應對距離晶圓邊緣1 - 2mm的先前被認為“最無關緊要”的晶圓區域。晶圓邊緣的表徵也必須在薄化後與圖案化晶圓的形狀 同時進行,以確保達到最佳的晶圓良率。

本文將介紹在極度晶圓薄化製程的探索和開發過程中所使用的在線量測方法。這些量測工具所提供的結果使我們能夠發現如何改進極度晶圓薄化的製程。同樣的量測技術可以用於驗證製程的改進,並在製程用於批量生產之後監控其穩定性。

量測方法

晶圓級干涉測量

為了測量FST、晶圓表面形狀和NT,我們使用了圖案化晶圓幾何系統(KLA-Tencor公司的WaferSightPWG)。這是採用雙重Fizeau的干涉測量系統,同時以解析度測量有圖案的晶圓正反面的高度。在測量時,晶圓垂直放置以減少重力引起的形變。晶圓正反面同時以「拍照」方式一次測量, 從而獲得所有訊息:表面形狀,平坦度和邊緣塌邊(edge roll-off)。

該量測儀專為測量晶圓表面形狀而設計製造並且具有1nm測量精度,過去在文獻[3]和[4]中已經被用於判斷晶圓表面形狀對CMP的影響,並確定CMP製程之後全晶圓的NT [5]。全晶圓NT可進一步區分在單個晶片範圍?,並且針對每個晶片給出範圍或峰谷值(PV)。

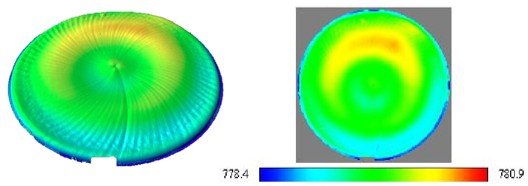

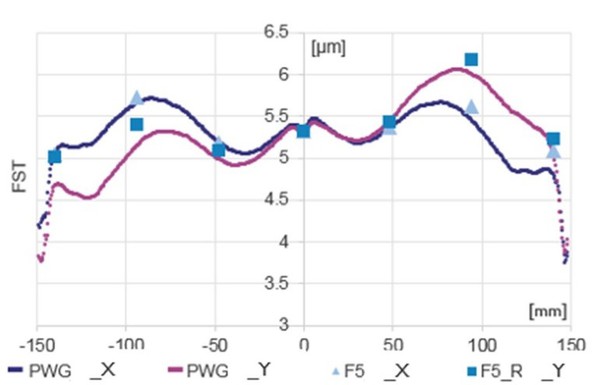

在本文中,圖案化晶圓表面形狀(PWG)系統在W2W接合和極度晶圓薄化期間被用於測量多個步驟之後的晶圓厚度,由此得出頂端晶圓在薄化之後的最終Si厚度。相對於之前採用電容式感測器所測量的晶圓絕對厚度, PWG提供的厚度結果是通過幹涉測量得出的晶圓相對厚度變化。該量測儀可以以高解析度提供晶圓厚度測量的2D和3D圖像,正如圖2所示。

| 圖2 : 在W2W接合之後所測量的3D(左)和2D(右)彩色晶圓堆疊厚度測量圖像,頂端晶圓被極度晶圓薄化至5μm。 |

|

晶圓邊緣檢測與量測

本文中所採用的全表面晶圓檢測和量測系統(KLA-Tencor公司的CIRCL-AP)包含一個邊緣檢測模塊。該模塊採用:(1)圍繞晶圓晶邊旋轉的激光掃描設置;和(2)橫向邊緣輪廓照相機,當晶圓旋轉時可以獲取晶圓邊緣的圖像。激光掃描包括激光、多通道光學元件和光電探測器/光電倍增管(PMT)。

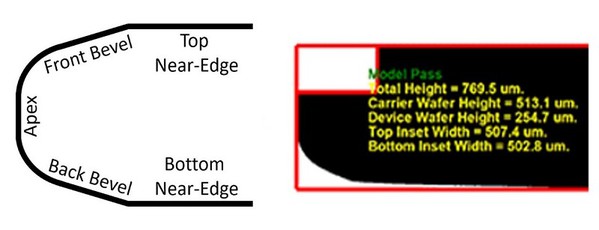

橫向邊緣輪廓圖像用於測量和量化邊緣形狀和邊緣修邊尺寸(見圖3)。基於邊緣形狀,計算出採用輪廓校正的旋轉光學器件的最佳軌跡,以確保在晶圓樣品上使用適當的入射光並獲得良好的信噪比。

| 圖3 : SEMI標準的晶圓邊緣形狀(左)和可以控制和測量的邊緣修邊輪廓(右)的橫向圖像。 |

|

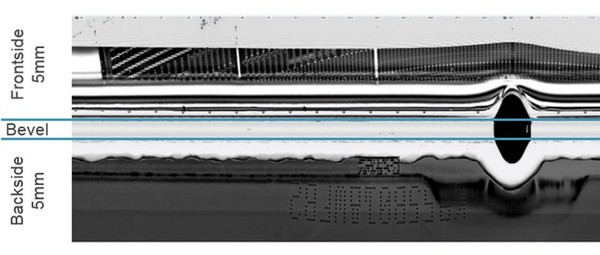

旋轉激光掃描儀同時使用明場、暗場和相位對比模式進行邊緣的檢測和量測,以捕獲多種晶圓邊緣缺陷類型,靈敏度可以達到0.5μm。該系統可以從包括晶圓邊緣的所有區域,即近邊緣(5mm)的晶圓頂部和底部、上下晶邊以及頂點以不同的對比度模式獲取圖像。 圖4顯示了包括凹槽在內的全晶圓邊緣檢測圖像的一部分。

| 圖4 : 明場邊緣檢測圖像的一部分,顯示了晶圓頂部和底部近邊緣(5mm)、上下晶邊以及頂點(圖像右側可以注意到凹槽) |

|

檢測基本上是通過比較切線上的相鄰像素來進行的。當像素的對比度或灰度值的差值超過某個用戶定義的閾值就被認為是缺陷的一部分。通過使用基於規則的缺陷分類技術,並通過定義關鍵區域和檢測區域,就可以通過實施的缺陷分類策略來實現高精度和純度的關鍵缺陷的分類。

量測偵測徑向線上的邊緣過度區,可以表徵晶圓邊緣上的層、膜或者其它線性特徵的覆蓋、同心度和均勻性。

前側檢查

全表面晶圓檢測和量測系統還包含一個前側檢測模塊,它使用:(1)延時積分(TDI)技術以及並行的明場(BF)和暗場(DF)檢測通道;(2)明亮的LED照明確保精度和穩定性;以及(3)一組通過程式可選用的光學物鏡,以提供不同的橫向解析度。

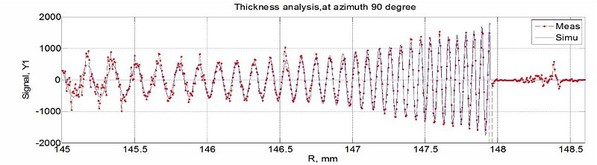

TDI照相機偵測薄化的Si頂表面和底表面的干涉訊號。圖5顯示了一個這種邊緣的例子。前側檢測模塊使用三個照明顏色(RGB),並產生三組干涉訊號,每組訊號具有其自己的特徵幅度和頻率。通過分析這些訊號,可以確定薄化晶圓邊緣處的Si厚度。正面檢測模組的高解析度光學元件能夠在邊緣快速下降時進行精確的厚度測量。

| 圖5 : CIRCL-AP前側檢測模組檢測到的干擾訊號的一個例子。條紋用於確定晶圓邊緣處的Si厚度。 |

|

結果

邊緣缺陷率

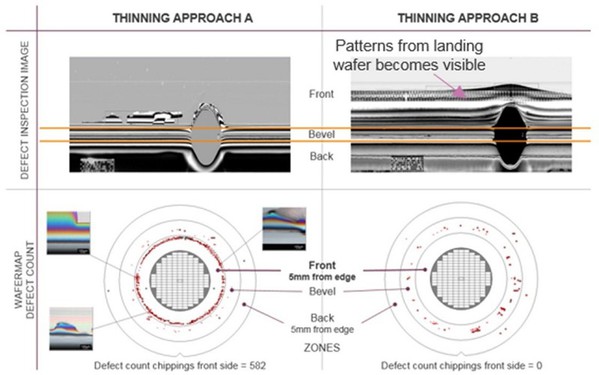

使用邊緣缺陷檢測和分類,可以針對磨削引起的損傷,邊緣切割和分層對晶圓薄化製程順序進行比較,並通過微調製程將關鍵缺陷的數量降至最低。

圖6顯示了經過兩種不同薄化製程順序的晶圓的自動化邊緣缺陷檢測的結果。通過將檢測區域放置在關鍵區域,即在頂端的薄化晶圓的晶圓邊緣附近,並且通過指定缺陷分類規則,檢測儀偵測到邊緣缺口,並相應地對其進行高精度分類。通過方法A所薄化的晶圓上檢測到的邊緣缺口的數量顯著高於通過方法B所薄化的晶圓上邊緣缺口的數量。使用方法B薄化晶圓時,邊緣完整性保持得更好。製程步驟的細節請參見文獻[1]。

| 圖6 : 用以比較極度晶圓薄化製程步驟的邊緣缺陷檢查結果。薄化方法A(左)在薄化後顯示出比方法B(右)更多的邊緣缺口缺陷數量。 |

|

當進一步探索薄化方法B時,詳細的邊緣檢查顯示,除了正常的晶圓變薄之外,薄化製程順序還引起了頂端晶圓的橫向收縮,導致來自底部的載體晶圓的圖案曝光,這可以圖6的右側檢測圖像上看到。

全晶圓厚度

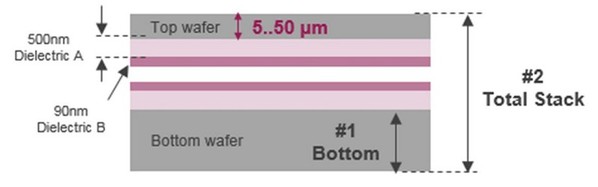

極度晶圓薄化製程中最關鍵的因素是精確控制FST及其變化,3σ重複性最大值為50nm,以獲得小於或等於0.1的精密度與允差比。FST由PWG測量,並且根據下面的等式得出: 接合和薄化後的堆疊晶圓測量厚度減去底部晶圓的測量厚度。

FST(x,y)= #2(x,y)- #1(x,y)- 2 x 0.59

該方程的不同組成如圖7所示。厚度#2(x,y)是W2W接合和薄化後總堆疊的厚度。厚度#1(x,y)是底部晶圓的厚度。最後,為了了解頂端晶圓的FST,還要從中減去頂端和底端晶圓上電介質的厚度。該厚度假設為定值,因為與FST的變化相比,電介質厚度的變化可以忽略不計。

| 圖7 : 頂端晶圓極度薄化後的永久性接合晶圓對的橫截面。FST是總堆疊的測量厚度中減去底端晶圓的測量厚度和電介質層厚度。 |

|

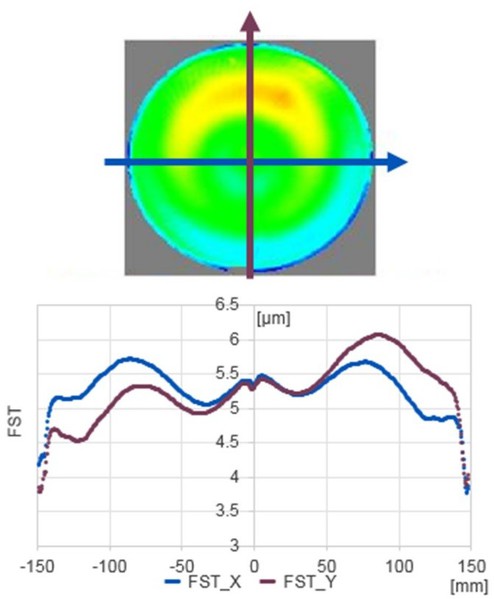

圖8顯示了在薄化製程之後PWG所測量的頂端Si層的厚度分佈。FST從中心至邊緣處大約有2μm的變化,在接近晶圓邊緣時有很強的梯度變化。在晶圓邊緣與晶圓邊緣2mm之間,採用標準晶圓量測工具來測量厚度輪廓變得很困難。這是由於機台所採用的晶圓邊緣排除以及量測波長在特定厚度的Si引起的不透光性。CIRCL-AP用於研究頂端晶圓的邊緣輪廓以完成FST的全晶圓表徵。結果詳情請參見以下章節。

| 圖8 : 頂端晶圓沿晶圓的X(藍色)和Y(紫色)軸的FST曲線。FST從中心至邊緣有約2μm的變化,在接近晶圓邊緣時具有很強的梯度。 |

|

如圖9所示,PWG測量結果與基於橢偏儀的標準測量結果具有明顯的相關性。與橢偏儀相比,PWG的優勢是可以測量晶圓上更多的點並達到更高產量,對於包含圖案的3D-SOC W2W晶圓接合的複雜堆疊,其結果也更可靠。

| 圖9 : PWG和標準橢偏儀的量測結果之間的相關性。 |

|

邊緣量測

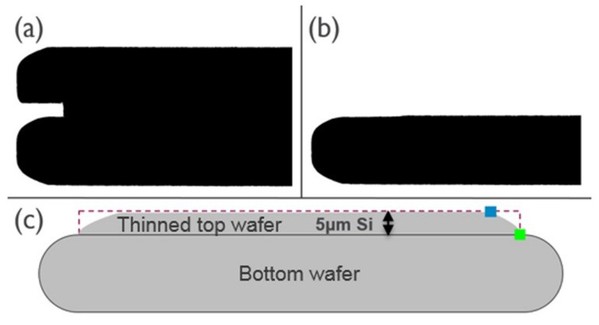

對於薄化之後的接合晶圓組的晶圓邊緣輪廓,由於頂部晶圓在接合之前的邊緣修邊(見圖10),預期頂端晶圓的FST會階梯式逐步減小。然而,當接近晶圓邊緣時,FST顯示出更為緩慢的降低。

| 圖10 : 邊緣輪廓圖像:(a)在薄化之前經過邊修邊剪的頂端晶圓置於底端晶圓之上; 和(b)極度晶圓薄化之後。圖像(c)顯示預期FST在邊緣修邊時的階梯逐步減小(虛線),但實際觀察並非如此。相反,FST提前開始降低(從藍點)到零FST(綠點)。 |

|

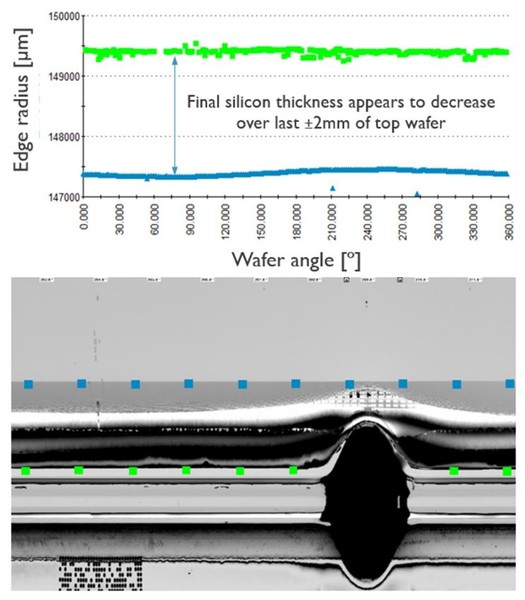

如圖11所示,CIRCL-AP能夠利用邊緣量測功能,檢測並報告最終的Si厚度開始減小的半徑。在對頂端晶圓進行0.5mm寬度的邊緣修邊時,預計可以看到頂端晶圓的頂部表面的均勻區域會延伸到半徑約為149.5mm。然而,實際從半徑147.5mm,FST已經開始向晶圓邊緣減小,這是在討論圖6所示結果時提到過的橫向收縮。

| 圖11 : FST從半徑147.5mm(藍點)處開始減小,到半徑149.5mm的邊緣修邊寬度(綠點)周圍的達到零厚度。 |

|

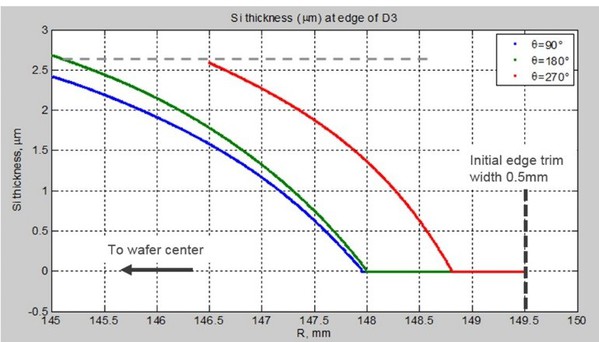

邊緣厚度

這個橫向收縮通過使用CIRCL-AP的前側檢測模塊,進行以晶圓邊緣為重點的詳細厚度測量得到進一步的確認。具有量測能力(計量檢測)的檢測儀器可以顯示厚度分佈,並如圖12所示,可以將厚度的減少量化為晶圓半徑R和角度θ的函數。從3μm到0μm處可以看到厚度逐漸減小,顯示在距邊緣2mm的環形內沒有Si留存,而初始邊緣修邊寬度僅為0.5mm。

| 圖12 : FST的減少表示為θ角的晶圓半徑R的函數。在距邊緣處2mm的環中沒有Si留存,而初始邊緣修邊寬度距離晶圓邊緣是0.5mm。 |

|

製程改進

頂端晶圓的FST輪廓和邊緣形狀通過使用前文所描述的量測技術進行表徵。為了實現穩定可靠的後穿孔製程並實現多晶圓堆疊,FST的變化需要低於1μm,並且需要將橫向的收縮減到最低。通過應用不同的硬件配置、製程調整,並使用本文所述的量測技術來驗證結果是否達到要求,優化晶圓薄化製程步驟的工作仍然在進行中。

結論

我們已經展示了兩種互補的量測儀的特性來表徵極度晶圓薄化製程的能力。這個量測儀組合還可以在量產環境中用以高產率來控制性能。在線AFM等技術可以協助進一步的偏移分析。對於3D-SOC整合技術方案,當Si減薄至5μm以下時,會出現多種挑戰,因而需要不同的測量技術來表徵整個晶圓的最終Si厚度。當進一步縮小3D互連尺寸並增加其密度時,對最終Si厚度以及總厚度變化(TTV)的良好控制將變得更加重要。

(本文作者M.Liebens,A.Jourdain, J.De Vos,T.Vandeweyer,A.Miller,E.Beyne任職於imec公司,Leuven,Belgium;S.Li,G.Bast,M.Stoerring,S.Hiebert,A.Cross任職於KLA-Tencor公司,Milpitas,California;原文發表於《第28屆年度SEMI高級半導體製造會議(ASMC 2017)》,Saratoga Springs, NY 2017.)

致謝

本文作者對Fumihiro Inoue,Nina Tutunjyan,Stefano Sardo和Edward Walsby表示深切的謝意,感謝他們提供用於檢測和測量的晶圓,並對結果做出解釋和討論,以及參與製程開發的早期量測。

參考文獻

[1] A.Jourdain,“Extreme Wafer Thinning Optimization for Via-Last Applications,” 3DIC,November 2016.

[2] F.Inoue,“Characterization of Extreme Si Thinning Process for Wafer-to-Wafer Stacking,”ECTC,May 2016.

[3] K.Freischlad,S.Tang,and J.Grenfel,“Interferometry for wafer dimensional metrology,”Proceedings of SPIE,6672,667202(2007).

[4] P.Vukkadala,K.T.Turner,and J.K.Sinha,“Impact of Wafer Geometry on CMP for Advanced Nodes,”Journal of the Electrochemical Society,158(10),p.H1002 (2011).

[5] L.Teugels,“Within-die and within-wafer CMP process characterization and monitoring using PWG Fizeau interferometry system,”ICPT,October 2016.

[6] C.Mehanian et al.,“Systems and Method for Simultaneously Inspecting a Specimen with Two Distinct Channels,”US Patent 7,782,452,issued August 2010.