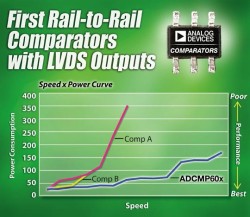

美商亚德诺的ADCMP60x系列轨至轨比较器是专为需要高速、低功率、轨至轨摆幅与高精密的应用而设。此一比较器系列支持所有盛行的数字输出级—包括LVDS(低压差动信号)、CML(电流模式逻辑)和TTL/CMOS(晶体管-晶体管-逻辑/互补金属氧化半导体)—为诸如医疗仪器、量测、RF(射频)和电信设备等应用所需。与LVDS兼容的输出级,专门设计用来驱动各种标准LVDS输入,让ADCMP60x比较器能与FPGA(现场可编程门阵列)以及ASSP(特殊应用标准产品)相匹配,以具有高速输入并达到更快的转换时间。

|

| ADCMP60x系列轨至轨比较器 |

ADCMP60x系列提供传播延迟,范围从1ns(奈秒)至35ns,以及少至2.5皮秒rms随机抖动。ADCMP60x比较器提供从2.5V至5.5V的轨至轨效能。

由于当过驱动情况为低的时候,从输出到输入的寄生耦合会导致不稳定,因此将输入到输出电源隔离很重要的。ADCMP60x系列家族的数个成员可分割二个电源以提供宽广的输入信号范围,且比起同级产品所减少的功率消耗达50%之多。高速栓锁与可编程磁滞特性是由一只单脚位控制选项来提供,产生平衡的输入-输出延迟并省却震荡的问题。

ADCMP60x比较器适合与ADI的DDS(直接数字合成)产品搭配应用,以产生可编程高速,低抖动频率。它们也与ADI的高速对数放大器互补,如AD8318,用以放大低位阶RF爆发式脉冲。