尽管EDA(电子设计自动化)大厂近年来持续致力于先进制程的开发工具的开发再辅以不断强化IP阵容的作法,这有助于缩短SoC(系统单芯片)的开发时程,但事实上,综观终端系统设计,混合讯号与模拟电路仍然是不可或缺的一环,身为EDA大厂之一的Cadence(益华计算机)仍然相当关注该领域的工具研发。

|

| /news/2014/08/08/1634210250S.JPG |

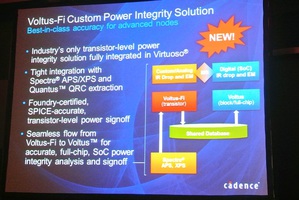

Cadence数字签核部门产品营销总监Jerry Zhao指出,综观芯片开发流程在进行验证(Verification)后,还有一道重要的程序,称为「签核」(Sign off)。它的功能类似于芯片设计流程的最后一道关卡,用于最后芯片设计的流程之用。在去年11月,Cadence就推出了以SoC为主的签核工具:Voltus,而在今年八月,Cadence正式发表Voltus-Fi,用作晶体管层级的电性测试,偏重模拟、混合讯号与电源管理等芯片。

Jerry Zhao比喻,将芯片视为一座城市的电网,电压在传输的过程势必会有电压不足的情形,这就必须透过升压方式继续传送电压,以让整个电网都能充分使用到电力。同理,芯片本身也会有类似的情形,一旦电压不足就无法驱动芯片运作,如此一来也会造成芯片本身的可靠度下降,透过Voltus-Fi的精准量测就有办法测出芯片内部各个部份的电性状况,避免在进入Type out的程序造成不必要的成本损失。

由于Voltus-Fi标榜精准量测的特性,Jerry Zhao不讳言,只要是内有晶体管的芯片皆能一体适用,像是内建ADC(模拟数字信号转换器)的MCU(微控制器)‧应用处理器、电源管理芯片、IGBT甚至是独立的ADC等,Voltus-Fi都有办法加测量,所以市场客户相当广泛。Jerry Zhao透露,ADI曾经就在3月的公开场合中,展示如何使用Voltus-Fi来进行产品开发,获得不少好评。

然而,Jerry Zhao也不讳言,这种产品概念,Cadence早在十几年前便已经提出,只不过先前Cadence历经了低潮期,这方面的投资研发力道便少了许多,不过在这两年左右的时间,Cadence又开始急起直追,相信要在签核领域中居于领导地位,只是时间上的问题。