超大容量FPGA的时代已经来临。ASIC原型设计和模拟市场对当前最大容量的FPGA需求格外殷切。有数家供应商提供商用现成(COTS)的ASIC原型设计和模拟系统,对於这些供应商而言,能够将当前最大的 FPGA 用於 ASIC 模拟和原型设计系统中,就意味着获得了显着的竞争优势。

|

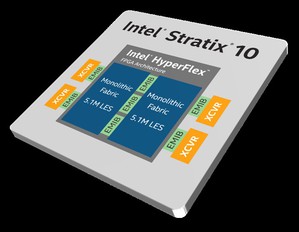

| 英特尔发布了全球最大容量的Stratix 10 GX 10M FPGA,拥有1020 万个逻辑单元。 |

模拟和原型设计系统旨在帮助半导体厂商在晶片制造前发现和避免代价高昂的软硬体设计缺陷,从而节省数百万美元的成本。原因是晶片在制造完成之後,解决硬体设计缺陷问题的成本更高,通常会需要昂贵的重新设计费用。当制造出来并交付给终端客户之後,解决这些问题的成本甚至会更高。正因为风险如此之高,且可能节省的潜在成本如此之多,这些原型设计和模拟系统为 IC 设计团队带来了真正的价值。因此模拟和原型设计系统的使用变得越来越为普及,因为在经济成本如此之高的情况下,没有哪个设计团队负责人会忽视这项谨慎的验证性投资。

英特尔发布了全球最大容量的Stratix 10 GX 10M FPGA,该产品是全球密度最高的FPGA,拥有1020 万个逻辑单元。这款元件密度极高的FPGA,是以现有的Intel Stratix 10 FPGA 架构以及英特尔先进的嵌入式多晶片互连桥接 (EMIB)技术为基础所设计。最新Intel Stratix 10GX 10M FPGA运用了EMIB 技术融合两个高密度Intel Stratix 10 GX FPGA核心逻辑晶片(每个晶片容量为 510 万个逻辑单元)以及相应的 I/O 单元。Intel Stratix 10 GX 10M FPGA其密度约为Stratix 10 GX 1SG280 FPGA 的 3.7 倍,後者为原Intel Stratix 10系列中元件密度最高的装置。英特尔的 EMIB 技术只是多项 IC 制程技术、制造和封装创新中的一项,正是这些创新能力,让英特尔得以设计、制造,并且交付目前世界上密度(亦即运算能力)最高的FPGA。

此外,包括英特尔在内的多家大型半导体公司都开发了自家的客制化原型设计和模拟系统,并在设计定案(tape-out)前使用该系统来验证其最大规模、最复杂、因此风险也最高的ASSP和系统单晶片(SoC)设计。ASIC 模拟和原型设计系统可以帮助设计团队大幅降低设计风险。因此,包括Intel Stratix 10 FPGA 和更早的 Stratix III、Stratix IV 和Stratix V 装置在内的Intel FPGA在过去十多年来一直被用为许多模拟和原型设计系统的基础装置。