瀏覽人次:【6635】

現代的嵌入式與運算系統,加入了高速匯流排、產業標準子系統,以及晶片中更高度整合的功能,逐漸變得更加強大。這些系統也變得更為複雜、對訊號品質更加敏感,排除問題的時間也變得更長。

高效能數位系統中經常使用的許多技術雖然存在著標準,主要的測試要求則可確保所有元件的同步化及整體無縫的整合效能。終端裝置可能包含多個子系統,這些系統有的需要與彼此和外界通訊。這是整合測試的延伸範圍,必須驗證整合功能的時序與子系統間的通訊。這項測試需要工具,除了對單一元件也對整個系統進行評估。

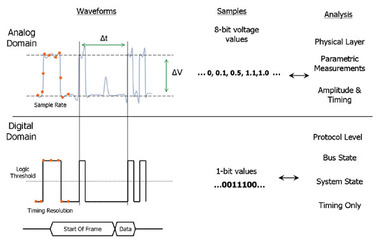

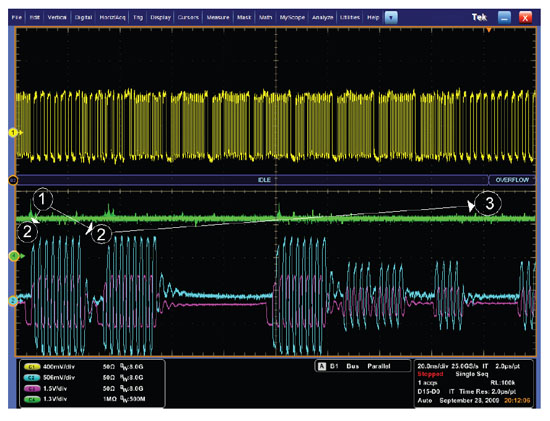

《圖一 類比與數位量測差異。》 - BigPic:599x383  |

《圖二 MSO70000可提供類比與數位訊號的時間關聯檢視。》

|

系統測試簡介

在增加功能與提升效能的過程中,工程師經常需要在設計中同時使用類比與數位訊號。這讓測試工作變得複雜,需要專用的工具,檢視待測裝置上各測試點的狀態。例如,類比測試需要精確的電壓值,以進行振幅、時序或眼狀圖量測等實體層分析。示波器一直是進行這項工作的主要工具。數位系統測試只使用邏輯狀態值,且僅可使用時序資訊。透過時間關聯,可進行許多數位訊號匯流排或通訊協定層級分析。數位系統測試與除錯可能需要對特定匯流排週期 (例如記憶體讀取或寫入) 進行觸發。具寬匯流排功能的邏輯分析儀,通常用於數位系統測試。

在許多情況中,當硬體與軟體工程師協力找出特定問題的根源,以排除問題時,會需要檢視匯流排的資訊,這些資訊同時包括電路圖和更高層次的抽象資訊(例如串列匯流排通訊協定的已解碼檢視)。許多設計擁有大量的硬體元件,用來執行特定工作,這些元件可能位於電路板的不同部位。為了檢視元件間的互動,工程師需要對待測裝置進行系統層級的檢視。工程師所面臨的挑戰在於確保元件運作同步化,這表示測試設備除了需能以更高層次的抽象與分析功能,檢視與分析資料外,也必須能夠提供關於時序效能的精確資訊。

混合訊號示波器(MSO)提供類比訊號特性分析功能,搭配數位匯流排事件與時序分析功能,可成為理想的系統除錯工具。混合類比與數位設計及驗證可受惠於三項主要的MSO功能:時間關聯、狀態能見度與資料驗證。

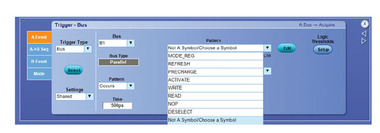

《圖三 使用使用者可定義的匯流排定義觸發。》 - BigPic:599x209  |

《圖四 記憶體讀取週期的匯流排合格觸發。》

|

類比與數位關聯

類比與數位訊號有時間關聯性,資訊可達成更具效率的驗證與除錯。在混合訊號控制系統中,軟體式的控制迴圈行為,可和類比激發與響應訊號建立關聯。在系統除錯中,錯誤的數位狀態 (例如無效的字元) 可更輕鬆地追溯到實體層中的低層級訊號影響 (例如資料相依的抖動)。

瞭解事件發生的背景,可在進行數位系統除錯時加以評估。例如,存取了哪個記憶體位置?這個資訊封包源自何處?發生匯流排故障時,ASIC的狀態為何?找出問題根源時經常需要低層級或實體層的詳細資訊,但是找出問題最具效率的方式,常常是瞭解更大系統所處的狀態。能夠在訊號通過系統時擷取數個檢視,可快速取得重要的深入解析。

分析特定類型週期經常是必要的,例如讀取週期間的訊號完整性,或是一排特定記憶體的寫入時序抖動。像是DDR中的精密訊號設計,會讓除錯變得複雜。當週期資訊散佈涵跨數個數位訊號時,需要精密的觸發才能即時加以回應。因此,有效的除錯,只有在特定匯流排週期期間才會包含訊號錯誤偵測。可對邏輯故障觸發類型套用數位碼型條件,以即時偵測訊號錯誤,例如讀取期間的突波。

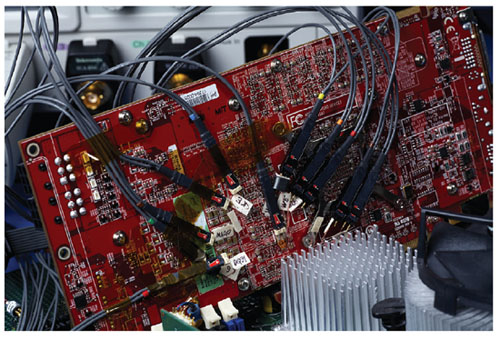

《圖五 P6780差動邏輯探棒連接至GDDR5視訊繪圖卡。》

|

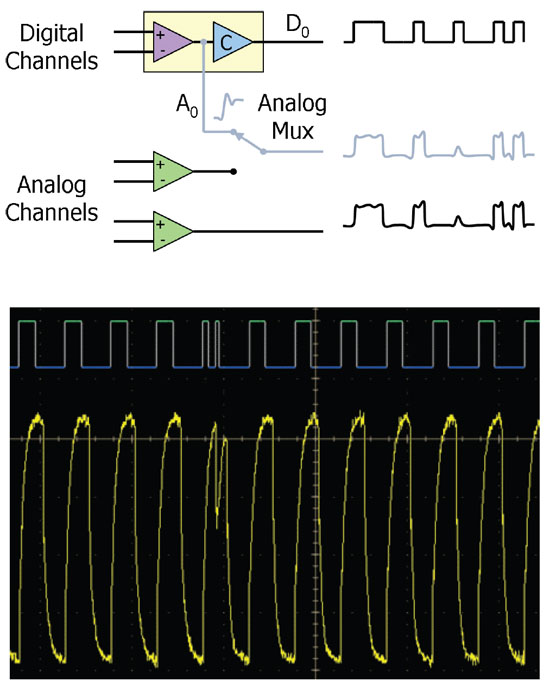

《圖六 類比多工器的方塊圖(上)。使用iCapture在數位與類比檢視中顯示的突波。數位與類比訊號同時都是從單一探棒擷取(下)。》

|

訊號存取

將探棒連接到裝置,會帶來另一項挑戰。裝置的實際小尺寸、電路板上需要探測的大量點數目,以及任何增加電容負載的探棒會改變裝置運作特性的事實,都是會增加探測挑戰的因素。探測解決方案專為需要能夠將電容負載減到最小而設計,讓工程師連接裝置更加容易,也能夠快速確定哪支探棒跟測試儀器畫面上的哪個軌跡有關聯。

MSO70000系列混合訊號示波器提供高效能的16通道邏輯探棒,例如P6780差動邏輯探棒。P6780可使用專用於焊入式連線的配件,連接至小型導孔與元件。

類比多工器

MSO70000系列包含iCapture類比多工功能,可讓工程師同時以類比與數位,檢視連接至16個邏輯探棒任一連線的訊號。iCapture功能有兩個重要的效益。同時以數位與類比域檢視訊號,不需要第一次的雙重探針探測。這可減少測試設備產生的電容負載,有助於確保待測裝置的最佳訊號完整性。第二項好處是任一16個數位通道皆提供更理想的時序與精密度。使用者可透過示波器的使用者介面啟動類比訊號,或是開發軟體常式,自動啟動或關閉類比多工器。

混合類比與數位裝置

混合訊號設計問題難以除錯,經常需要涵跨多域的先進量測技術。MSO70000同時提供了類比與數位訊號分析功能,檢驗目標系統中的硬體與軟體互動。下列三個例子,使用了MSO70000進行混合類比與數位系統除錯,包括高速串列技術、FPGA設計和RF子系統。

高速串列設計

高速串列匯流排架構,包含PCI-Express、HDMI與SATA,可提供大量資料傳輸率,還有差動訊號、減少的接腳數量,以及電路板配置佔用空間變少的優點。這些最新標準的共通點是更快速的邊緣速率,以及更窄的資料脈衝,為設計人員帶來了獨一無二的嚴格要求。隨著multi-gigabit資料速率在數位系統中的普及,訊號完整性(積體電路之正常運作所需的訊號品質)也成為設計人員的首要考量。資料串中若有一個錯誤的位元,就會對指示或執行結果造成重大的影響。

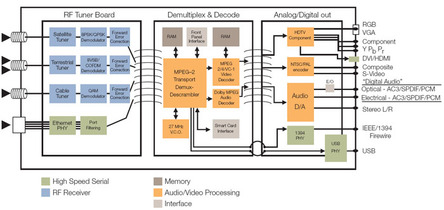

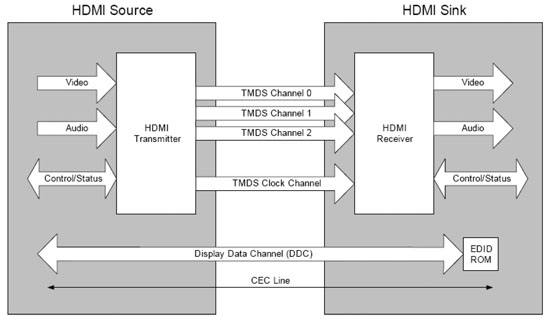

高效能視訊系統可加入各種廣泛的技術,例如RF接收器、視訊處理器、記憶體和高速串列介面。圖七顯示高階機上盒的典型方塊圖。這個系統建置了HDMI介面,此一介面以3.4 Gb/s的速度各涵跨三個資料通道運作。圖八顯示HDMI連結的架構,包括高速時脈與資料線,以及在標準模式(10 MHz)中使用I2C訊號的顯示資料通道(DDC)。DDC線路是用來進行來源(發送器)與終端(接收器)裝置間的資訊交換。

《圖七 典型高畫質機上盒的方塊圖。》 - BigPic:699x330

|

《圖八 HDMI 系統架構。》

|

《圖九 I2C SDATA 線上的突波。》  |

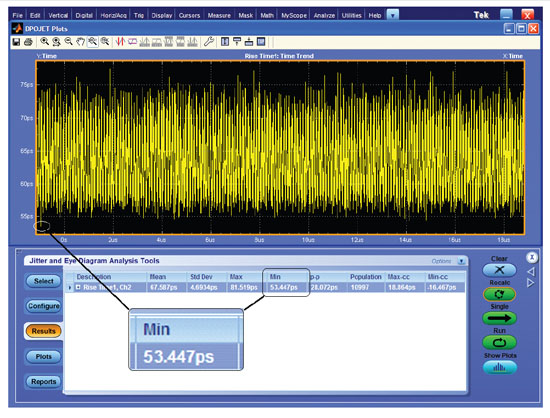

《圖十 靠近 I2C 突波的 19 us 區間內的上升時間趨勢圖。量測到的最快速邊緣速率約為 53 ps。》

|

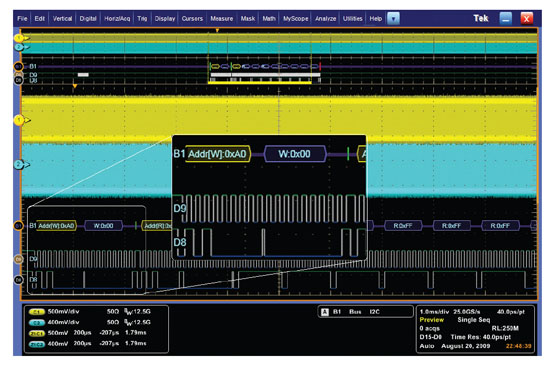

《圖十一 MSO70000 在串音問題解決後解碼位址 0xA0。》

|

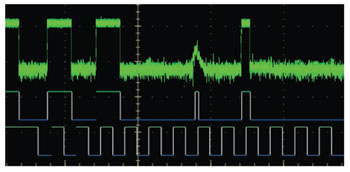

這項設計需要除錯,因為至監視器的輸出會間歇性地關閉。首先檢查實體層的功能運作,接著讓各通道通過眼狀圖與抖動量測。量測高速時脈與資料線後,會監控 I2C控制線是否有錯誤碼或無效資料。正常運作時DDC使用位址 0xA0和0xA1。但是在MSO70000擷取和解碼I2C傳輸資料後,有時會在待測物開機時驗證到不正確的位址。圖九使用MSO70000上的iCapture工具,以數位和類比格式顯示的SDATA線。根據類比訊號檢視,似乎是串音或其他雜訊的耦合效應,讓I2C傳輸資料變成亂碼。

為了找出突波問題的根源,會分析鄰近的通道,並評估涵跨各高速通道的邊緣速率。圖十顯示靠近突波發生邊緣的19 us時間區間趨勢圖。這項分析提供了對訊號異常根源的一些深入解析。最低量測的53 ps上升時間,比HDMI系統中常見的 90至100 ps邊緣速率快上許多。這項設計接著經過修改,以顯示邊緣速率,並改良資料與時脈屏蔽線。圖十一顯示正確的I2C異動,包括位址0xA0和0xA1與寫入(Write)資料前的確認位元。

現場可編程閘陣列(FPGA)

由於設計尺寸與複雜度日新月異,讓設計驗證程序成為今日FPGA系統的關鍵設計瓶頸。內部訊號存取受限、先進的FPGA封裝技術,以及印刷電路板 (PCB)電子雜訊等,都是讓設計除錯及驗證,變成設計週期中最困難程序的關鍵因素。

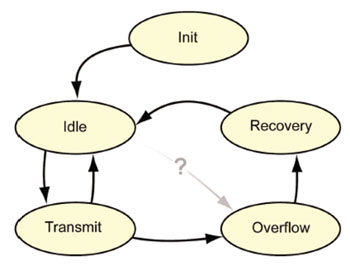

《圖十二 PCI Express 接收器的除錯埠 (Debug Port) 狀態機器。》  |

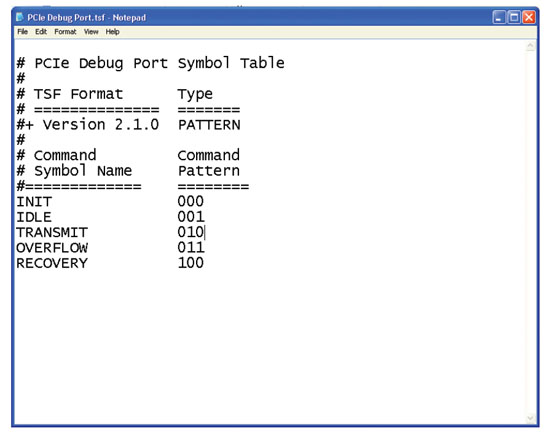

《圖十三 PCIe除錯埠(Debug Port)適用的Tektronix符號檔。》

|

當FPGA架構設計發生錯誤時,除了顯示FPGA邏輯內部狀態的數位線之外,工程師還可使用MSO70000 來檢視輸入與輸出訊號等類比事件與電源供應線。可進行除錯的可能問題包括:

●模擬中未考量到的情況,例如電源供應問題

●較強大的線路驅動器影響鄰近線路所造成的高速線路間串音 (只有發生在一組驅動器同時啟動時的情形)

●不正確的軟體指令傳送到狀態機器,造成未預期的行為

●狀態機器邏輯錯誤、解除鎖定的相位鎖定迴圈,以及FIFO溢滿

對於PCI Express連結與DDR記憶體匯流排間用來做為接橋的FPGA,讓我們檢視MSO70000如何能夠對其進行除錯。這項範例顯示從外部監控FPGA狀態,如何可加速FPGA狀態機器問題的除錯。

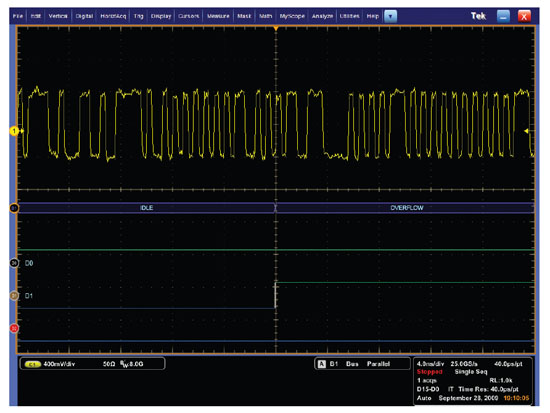

PCI Express發送器/接收器對經常不只包括串列連結,也包含內建「除錯埠」。這種並列輸出能夠提供即時的資料,摘要說明裝置內發生的異動。在發送器和接收器上設置除錯埠,能夠讓開發人員監控傳輸連結狀態是否良好,並在連結的發射端或接受端上找出許多類型的問題。圖十二顯示PCI Express串列接收器中可能配備的狀態機器。此處顯示的簡化互動,象徵了例行連結程序,黑色箭頭表示合法狀態異動。圖十三為擷取畫面影像,顯示以記事本(Notepad)建立的範例 Tektronix符號檔(.tsf),以進行對MSO70000上除錯埠的分析。圖十四顯示取自 PCI Express串列連結的擷取資料。匯流排上的錯誤造成MSO觸發匯流排違反。由於良好的訊號品質,可以目測得知問題並非來自基本的類比問題。圖十四中的發現強烈暗示邏輯問題是由時序問題或其他數位衝突造成。

由於串列資料錯誤符合除錯埠上的Overflow(溢位)狀態,又由於串列資料是由 SERDES (串列化/解串列化)所驅動的,因此推估問題與時序有關,並且起源自 SERDES 之內,是合理的假設。此時在架構考量或其他除錯觀察結果的影響下,或許有數種可能的疑難排除策略。

《圖十四 匯流排錯誤(OVERFLOW狀態)與除錯埠(Debug Port)狀態機器中的錯誤狀態變更同時發生。這意味著SERDES內的€時序問題,這項問題可能來自FPGA合成過程中的錯誤。》

|

《圖十五 接地雜訊(1)造成對Read資料(2)的設定與違反時間保持,而傳回無效的資料至PCIe匯流排。》

|

FPGA是為了將自身轉換為程式設計人員所定義之功能元件而設計。「轉換」程序稱為合成,因為它真的會使用其內部閘極合成想要的函數。知道這一點後,聰明的設計人員就會在FPGA合成結果上連按兩下,先進行錯誤的疑難排除,以確認所有狀態機器的時序轉態都已正確執行。

如果這樣無法顯示出問題的來源,第二個務實的步驟是將其他訊號傳送至除錯接頭,以追蹤裝置的行為。例如,在評估過圖十二中所示的Current State(目前狀態)資料之後,FPGA可能會重新編製程式,以提供除錯埠「Next State」(下一個狀態) 的資料。這樣可能會顯示出Current State (目前狀態)中沒有看到的問題,而且當然也可以調查更多除此以外的狀態。

進行FPGA設計除錯的另一個常見方法,是讓資料從錯誤源反向流回,以找出問題根源。在進一步調查後,MSO70000可顯示電源供應線造成了DDR記憶體匯流排上的雜訊。就在FPGA狀態機器之前,讓PCIe連結進入記憶體讀取(Read)要求發佈的閒置狀態。切換雜訊造成記憶體匯流排的問題,進而傳回PCIe匯流排,這是導致FPGA狀態機器錯誤的主要原因。

追蹤系統問題的工作,常常不單是循著突波,回溯其位於某個邏輯元件中的根源。單一匯流排上的錯誤,其根源以及影響範圍可能包含系統中的多個匯流排。因此,完整的跨匯流排分析已經成為不可或缺的疑難排除方法。使用 MSO70000,可在共用的螢幕上顯示時間關聯的數位與類比事件,在對FPGA與多匯流排系統進行疑難排除時,提供強大的新工具。跨匯流排分析可讓您看見整個系統中同時發生的交互作用,不但加快錯誤的追蹤,還能更快找出其根源。

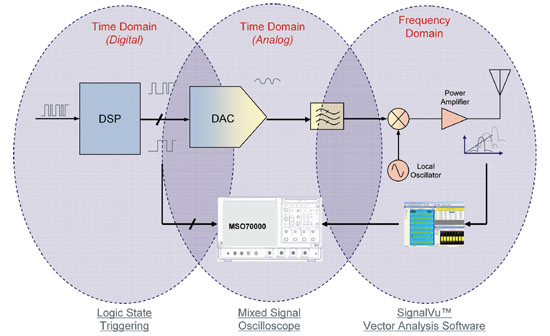

《圖十六 發送器的方塊圖,以及至混合訊號示波器的連線能力。》

|

射頻測試

設計軟體定義無線電的挑戰之一,是針對硬體與軟體錯誤進行疑難排除與解決問題。隨著DSP控制越來越多的類比功能,設計數位基頻中的非法狀態或濾波值,在傳播到發送器的濾波與放大器部位時,會成為RF頻譜錯誤。

圖十六顯示MSO的連線能力,適用於複雜的多域分析。不僅能夠分析數位域和類比域,若加入向量訊號分析軟體,可對同一次資料擷取進行包含頻域的詳盡分析。

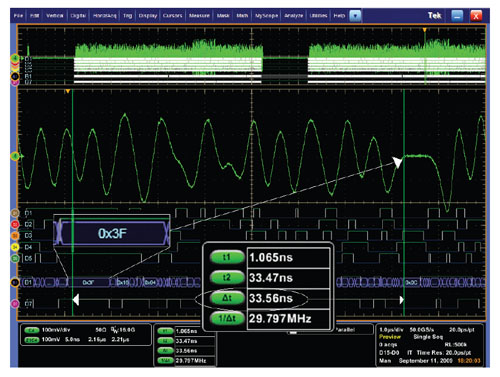

在本範例中,設定了MSO邏輯觸發,以擷取至數位對類比轉換器(DAC)輸入的非法狀態值。全部皆為「1」的狀態值(0x3F)邏輯觸發,會觸發擷取。圖十七中的類比訊號關聯檢視顯示約34 ns的時間延遲,這代表此一高速裝置DAC轉換過程中的絕對延遲。

《圖十七 DAC 的邏輯狀態與類比輸出的整合式檢視。》

|

《圖十八 SignalVu 可提供時間關聯的多域檢視,以進行深度分析。》 - BigPic:599x452  |

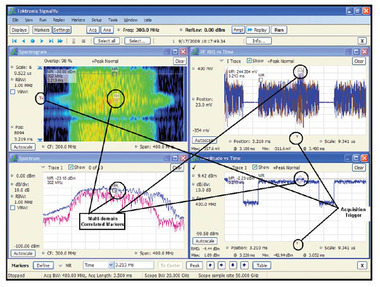

這項分析可將MSO類比通道上出現的寬脈衝,與邏輯狀態建立關聯。RF訊號的時域檢視,可能無法提供對軟體無線電設計造成影響的完整檢視,因此需要進一步的RF效能關聯分析。

若要評估同一次擷取的訊號RF效能,可對相同的資料集直接使用SignalVu 軟體。圖十八顯示對圖十七擷取的同一個資料集進行RF分析,使用了邏輯狀態觸發來觸發資料集,並利用SignalVu分析進行RF分析。

在本範例中,進行了離散傅立葉轉換(DFT),以顯示頻譜圖並進行頻譜頻域分析,並將時間取樣資料,以RF I&Q對時間及振幅對時間的格式顯示。

已開啟時間關聯標記,以顯示RF分析的時間關聯,提供不同的檢視,我們可清楚看到,DAC處發的非法狀態值,造成了RF的頻譜再生。RF再生可追溯回方塊圖中的數位狀態,進而排除發送器類比部份的硬體問題。

結論

數位設計人員需要快速地找出與分析廣泛的問題,涵蓋範圍從串音或抖動等訊號完整性問題,到設定與違反時間保持或遺失封包等匯流排錯誤。MSO70000系列具備80 ps時序解析度,可同時對多達20個通道,進行精確的時序量測。使用iCapture,可以快速檢視數位通道的類比特性而不需新增另一支探棒,可節省時間,並將待測裝置上的負載降到最低。透過對匯流排觸發與解碼,可快速偵測到無效狀態。

高效能的數位系統持續演進,變得越來越複雜、對訊號品質更加敏感、排除問題所耗費的時間也更長。MSO可以成為適合的工具,協助以有效率的方式,對系統進行分析與除錯,用前所未有的速度讓產品上市。

|