在以要求為基礎的模擬測試當中,有一部分的設計可能會因為細微的設計錯誤、不完整的測試、或者遺漏的要求而沒有運行。本文以範例闡述三重選擇演算法的設計測試,因為要求的遺漏而被認定為不完整的重要環節。

對Simulink設計進行有系統的測試,可以幫助確保在產生程式碼之前能夠對設計的預期與非預期行為更有把握。在以要求為基礎的模擬測試當中,有一部分的設計,可能會因為細微的設計錯誤、不完整的測試、或者遺漏的要求而沒有運行。模型測試的覆蓋度可以藉由測量有多少的Simulink設計確實在測試過程中執行,來協助確認這些測試的缺口。

要求遺漏是在以要求為基礎測試過程中模型測試覆蓋不完整的一種常見的原因。這種類型的模型測試覆蓋遺漏,通常是因為有些設計元件無法被追溯到更高層級要求。收集模型測試覆蓋可以協助處理這樣的情況。本文將闡述範例,其中的三重選擇(triplex selection)演算法的設計測試,因為要求的遺漏而被認定為不完整。

三重選擇演算法:概述與要求

三重的訊號選擇演算法常使用於航太控制系統軟體。在三重訊號選擇,會由三個獨立感測器「投票」選出一個訊號,然後在飛行器的控制使用這個被選擇出來的訊號。當一個感測器沒有被偵測出任何故障,則該感測器會被視為「有效」。

在這個範例,要選擇的是飛行器的空速(Airspeed)訊號。空速訊號選擇演算法的要求如下:

‧ HLR_1 從三個感測器選擇空速訊號:當三個空速感測器皆為有效時,飛行控制電腦應選擇三個感測訊號的中間值。

‧ HLR_2 從兩個感測器選擇空速訊號:當只有兩個空速感測器有效時,飛行控制電腦應選擇兩個感測訊號的平均值。

‧ HLR_3 從單一感測器選擇空速訊號:當只有一個空速感測器有效時,飛行控制電腦應選擇有效的訊號。

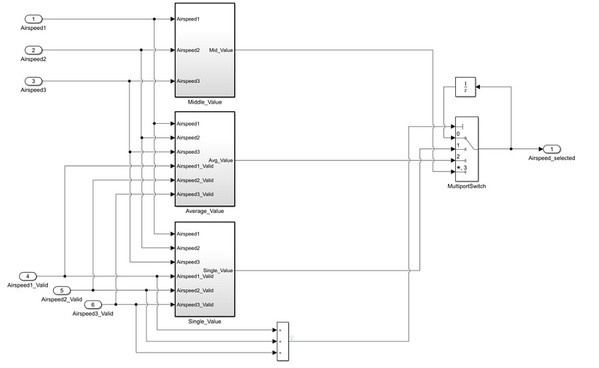

圖1呈現了這三項要求在Simulink的執行。

| 圖1 : Simulink執行空速訊號選擇演算法。 |

|

執行演算法並收集模型測試覆蓋測量資料

在模型內一個專用的子系統執行每一項要求,並且為每一次的執行撰寫單獨的測試案例。在執行這些測試之前,需要確認模型測試覆蓋的測量資料有被記錄下來。

模型測試覆蓋的測量資料可以是個別的(為單一測試收集)或累計的(多次測試的總計)。我們會收集以要求為基礎的測試的累計覆蓋來衡量設計是否在完整的測試套件完全地執行。

模型測試覆蓋的衡量有許多類型,像是執行覆蓋(execution coverage)、判斷覆蓋(decision coverage)、訊號範圍覆蓋(signal rage coverage)、以及關係邊界覆蓋(relational boundary coverage)。在這個範例,我們關心的是判斷覆蓋,也就是一種測量在模型中執行所有可能的邏輯結果來進行判斷的結構覆蓋。如果所有被送到切換開關(switch)的輸入值,在模擬當中至少被選擇了一次,則像是Switch blocks等Simulink模型物件會接收完整的判斷覆蓋。

我們使用Simulink工具列Apps頁籤下的Coverage Analyzer app啟動模型測試覆蓋的收集(圖2)。

開啟了Coverage Analyzer app,可以使用Coverage頁籤下Coverage ON/OFF按鈕來的開啟覆蓋資料的收集。此外,也使用Cumulative Collection按鈕來啟動累計的覆蓋。接著在覆蓋的收集被啟動的狀態下按下現在被標記為Analyze Coverage 的Play按鈕來模擬模型(圖3)。在每一次的模擬使用不同的測試向量來模擬數次。

| 圖3 : 覆蓋收集已被啟用的Coverage Analyzer app。 |

|

圖4為覆蓋的結果。綠色標示的區域表示模型測試覆蓋完整,包含每一個子系統內的所有的模型物件,紅色區域則代表覆蓋完整度不足。

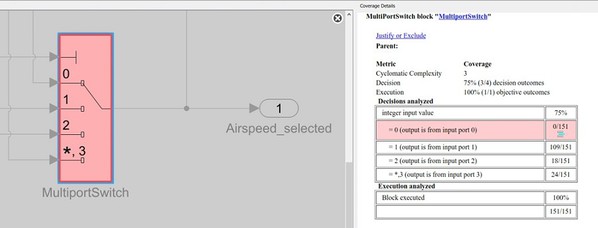

判斷覆蓋似乎在Multiport Switch block遺漏了。為了了解發生的原因,打開Simulink的覆蓋細節(Coverage Details)窗格,檢查個別模塊模型測試覆蓋細節(圖5)。

| 圖6 : Multiport Switch模塊的覆蓋細節窗格 |

|

第一個送到Multiport Switch的輸入值在模擬當中從未為0。回想圖1的模型,當時第一個送到Multiport Switch的輸入值為有效訊號的數值。由此可見,並沒有測試到所有的空速訊號皆為無效的案例。

這項遺漏的模型測試覆蓋是因為缺少了更高層級的要求。沒有要求指出在未有任何空速訊號為有效的情況下,仍然必須選擇出訊號。然而,看起來設計已經納入了處理這類情況的邏輯。

因此,加上了這項遺漏的要求:

‧ HLR_4 無有效感測器時的空速訊號選擇:當三個空速訊號皆為無效時,飛行控制電腦應暫停空速訊號的選擇。

接下來,加上一個新的測試案例並重新執行測試。這時達到完整的判斷覆蓋(圖7)。

如同這個範例所示,模型測試的覆蓋是一項確認在以要求為基礎的測試當中是否有要求遺漏的可靠方法。可以使用模型測試覆蓋的結果,以確保設計之中正確部位的運行。

另一種模型測試覆蓋不完整常見的原因為死邏輯(dead logic)。「死邏輯」指的是Simulink模型或Stateflow圖表,其中任何一個部分從未在模擬過程中被執行,例如一個送到Switch模塊的輸入值可能從未被選擇,或者一個狀態機的轉換可能從未被採用。

最佳的實作途徑是在編寫或執行以要求為基礎的測試之前,先使用Simulink Design Verifier(為Simulink設計驗證工具)來分析模型,並且解決死邏輯的情況。也可以使用Simulink Check(為Simulink驗證標準檢測工具)裡面的Model Slicer功能,進行死邏輯的調整或除錯。

(本文由鈦思科技提供;作者Pat Canny任職於MathWorks公司)