為了推動晶片市場邁向1nm世代,本文上篇介紹了前段、中段與後段製程的主流技術及其面臨的挑戰,並進一步探討這三大製程模組中更具創新的其他技術;下篇則將延伸至更進階的製程技術開發,集結愛美科不同邏輯元件研究團隊的見解。

創新製程技術

後段製程:混合金屬佈線、半鑲嵌製程

為了與前段製程的微縮進度維持同調,在最關鍵的局部導線層(M1與M2)上的金屬導線間距最終也會縮減至21nm。這些層片之間的通孔(via)臨界尺寸也就必須小至12~14nm。

在傳統的銅雙鑲嵌整合方案中,阻障層與襯墊層(liner)在實際進行銅佈線前就會被沉積在通道(trench)與通孔內,但是,如果要以如此緊湊的尺寸製造晶片,阻障層或襯墊層會太佔空間,導致用來填充銅的空間不足。這會對通孔的電阻與變異性(variability)產生負面影響,且已變成微縮的限制。

此外,由於晶片設計對高電流密度的要求,電遷移的可靠度(reliability)也面臨挑戰。混合金屬佈線(hybrid metallization)是解決這項挑戰的方式之一。在這套架構中,通孔採用替代金屬,例如釕(Ru)、鎢(W)或鉬(Mo),並連至晶片底部的銅線,完全不需阻障層。如此,銅線障壁能變得更薄(2nm),同時維持電遷移的可靠度,並降低通孔的電阻。

儘管就電阻而言,這個方法頗為誘人,但是否能同時具備可靠度—這也是為了要發展成解決方案而正熱烈投入的研究領域,仍是關鍵。

為了將導線間距減至21nm以下,愛美科提出了半鑲嵌製程,成為引人注目的方案。其關鍵在於控制電容時容許互連導線增加高度,進而促使整體電路的電阻電容(RC)值獲益。

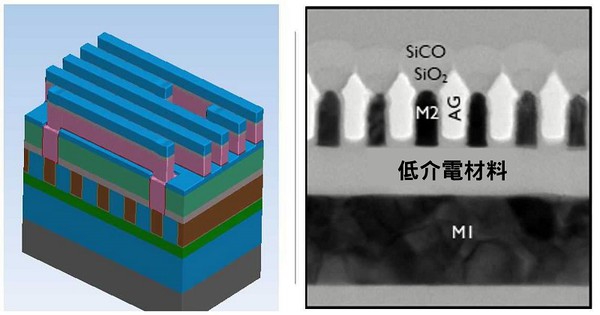

| 圖七 : 半鑲嵌製程模組的示意圖(左圖)以及其掃描式電子顯微鏡(SEM)影像(右圖)。 |

|

在製程技術方面,半鑲嵌製程採用可圖形化的替代金屬材料,最終還有氣隙(airgap)。而與雙鑲嵌製程相比,其根本差別在於省去金屬材料的化學機械研磨(CMP)—在雙鑲嵌製程,那是最後一道步驟。

在半鑲嵌製程,通孔以單鑲嵌的方式進行圖形化,接著進行以金屬填充,然後過度填充(overfill)—意指繼續沉積金屬,直到介電層上方形成一層金屬層(也就是不含阻障層的金屬層,像是Ru或Mo)。接著再進行光罩、蝕刻來製造金屬導線。這樣就能產出比雙鑲嵌製程還要高深寬比的導線,從而降低電阻。金屬圖形化之後,導線之間的間隙可用介電質填充,或是當作局部導線層的局部氣隙(partial airgap)。

預計到了第二代的半鑲嵌製程,就能製出全局氣隙(full airgap),且有序金屬合金也有可能在後段製程的後續階段中被用來當導體。這一連串的措施可以實現世代更迭的漸進改良。運用氣隙,就能抑制因採用高深寬比導線所帶來的電容增加。

半鑲嵌製程預計會用來製造最關鍵的金屬層M1和M2,還能在上面那些重要性相對較低的互連導線層中,與傳統的雙鑲嵌製程或混合金屬佈線方案整合。

中段製程:微縮加速器推動的連接性革命

為了提升佈線性,在中段製程已經可以看見結構性的微縮加速器獲得採用。這種連接性(connectivity)的演化—或說是革命將會持續,並開放中段製程導入其它分層,端視元件與互連導線之間的連結需求而定。舉例來說,叉型片的元件架構就能實現彈性更高的閘極連接與截止,進而增加佈線彈性。

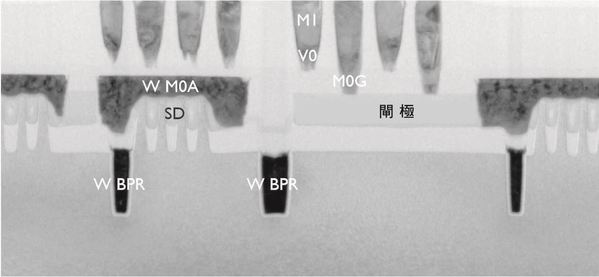

埋入式電源軌(puried power rail;BPR)則是另一項新興技術。電源軌是電力傳輸系統的一部份,且通常用於晶片的後段製程,也就是Mint與M1金屬層。埋入式電源軌正好相反,於前段製程埋入,以有利於釋出互連導線的佈線資源。

埋入式電源軌架構充滿挑戰性,並直接影響了前段與後段製程。在2020年超大型積體電路研討會(VLSI 2020)上,愛美科在FinFET CMOS的測試晶片上展示了一套基於鎢(W)的埋入式電源軌整合方案,並未對CMOS特性產生負面影響。其他的互補評估研究亦顯示,在邏輯與SRAM的晶片設計中導入埋入式電源軌來當作微縮加速器,可以提供系統級的優勢。

這套整合方案還能以所謂的VBPR架構進一步擴充。在VBPR架構中,連至埋入式電源軌的通孔與中段製程的分層(M0A層的導線)壓合。愛美科團隊在VLSI 2020上展示了鎢基的埋入式電源軌方案,將Ru通孔(即VBPR)用來當作埋入式電源軌與M0A層Ru導線的接面。該方案在電阻與電遷移方面獲得了優異表現。

| 圖九 : 整合鎢基BPR導線與FinFET矽晶片的穿透式電子顯微鏡(TEM)影像。 |

|

此外,要進一步降低源極與汲極的接觸電阻,還需要更多創新。愛美科已經提出了優化的接點方案,包括以原子層金屬沉積製成的環繞式接點,用以作為鑽石磊晶接點的替代方案,它能再度擴展接點面積,嚴格來說這樣就能降低接觸電阻。

續進1nm節點 延伸更多開發選擇

前段製程的CFET:通往3T邏輯標準單元的途徑

對5T以上的架構來說,要進一步降低元件高度,主要受限於佈線性問題—這應該要在邏輯區塊級進行檢視。為了優化佈線性,我們採用了互補式場效電晶體(complementary field effect transistor;CFET),進而擴展摩爾定律的極限。

CFET的概念是將nFET以鰭對鰭(fin-on-fin)或片對片(sheet-on-sheet)的方式摺疊於pFET之上,從真正的意義來說,也就能完全利用以3D方式進行元件微縮的所有可能。

該架構的最大優勢在於尺寸微縮,最終能將3T邏輯標準單元與SRAM單元的電路佈局面積銳減。

愛美科在VLSI 2020已展示首個實驗性概念驗證的CFET元件,以單晶製造。該研究團隊成功克服了這套複雜的製程方案中的嚴峻挑戰,CFET在塊材基板上「從腳到頭」製成。

目前,序列CFET製程(sequential CFET)也在研究中,以作為製程複雜度較低的替代選擇。在序列CFET製程,在生成最底層的元件(例如pFET)之後,會接續進行晶圓接合,以產生最上層元件(例如nFET)的通道,接著才是製造最上層元件。序列CFET提供最上層元件更彈性的通道材料選擇。

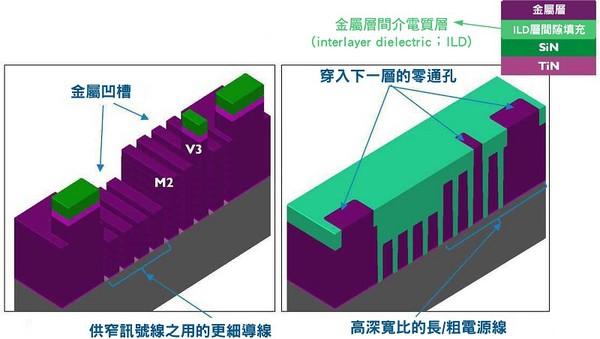

後段製程:「併合通道高度零通孔」與探索替代導體

在後段製程,金屬導線與通孔的電阻與電容仍是最重要的參數。解決方法之一是採用替代的金屬佈線架構,通常被稱為「併合通道高度零通孔」(hybrid-height with zero via;H2 with zero via)。根據金屬導線的不同應用需求,該方案能靈活地以電阻換取電容。

其概念是將每層金屬層細分成三個獨立的子層(sub-layer):中間導線層,以及可向上或向下延伸的分層。每層金屬層現在就有四種可能:

1.單一中間導線層

2.中間導線層與下方延伸層

3.中間導線層與上方延伸層

4.中間導線層與上下方延伸層

如此一來,就能在相同的焊裝面積下調整金屬導線的高度與深寬比。舉例來說,如果要將某導線當作電源軌—會對電阻極為敏感,那麼就能以高深寬比(因而具備低電阻)來製造;但要是該導線需要傳輸訊號,那麼就只會採用中間導線層,以維持低電容。這套架構不僅提供以電阻換取電容的彈性,預計還能提升整體電路的能耗與傳輸速度。

從製程的角度來看,不同的通道高度可以透過金屬凹槽蝕刻(recess etching)來製成。透過掘入一條直通到底的凹槽,就能用來當作垂直的通孔接線,因此就不再需要傳統的通孔結構。愛美科目前正在處理「併合通道高度零通孔」架構的製程所帶來的各式挑戰。

| 圖十一 : 用於第二層金屬層(M2)的「併合通道高度零通孔」架構概念圖。 |

|

此外,將標準單元面積縮至3軌~4軌,就需要電阻極低的導體。愛美科探索了無數種新穎的導體材料,它們必須比Ru與Mo具備更好的優勢。這裡 所謂優勢,指的是整體電阻與金屬內部載子平均自由路徑(mean free path)的乘積。受到關注的是有序的二元介金屬化合物,要在極度微縮的尺寸下具備低電阻,例如釕基或鋁基化合物—如AlNi或RuV3就屬於這類,雖然這兩者皆非唯一選項。

全始計算的結果顯示,多種金屬在將來的互連導線應用上具備富有前景的特性。尋找下一代的新興導體並不容易,但令人振奮的是,世界各地已有數個研發團隊開始接受開發新興材料的想法,並在找尋合適的選擇。

就更長遠來說,異質的石墨烯/金屬導體也是有趣的替代方案。我們知道石墨烯的原子結構很薄,且具備良好的導電與導熱特性。然而它無法保有充足的載流子,因此不能用來當作局部互連導線。

但其實還是有辦法來調節石墨烯的傳導性。其中一個方法是利用異質的金屬/石墨烯方案,將金屬(如銅、釕、鉬等)封裝在石墨烯之內。愛美科稍早驗證了這種異質方案能夠達成低電阻與高熱穩定性。

中段製程

為了進一步紓解佈線壅塞的問題,並滿足新興電晶體架構的需求,中段製程需要更進一步創新。例如,CFET所需的創新解決方案會關注在閘極接點—如今這在nFET與pFET元件中相當常見。

此外,高深寬比的通孔會將不同結構單元互連—這些單元現已擴展至3D結構。然而,這些深通孔的主要寄生電阻也需調降。透過導入先進的中段製程接點(例如材料選用Ru),就能實現上述目標。

結語

隨著微縮推進至5nm以下,晶片製造商可能會漸漸放棄採用主流技術,像是前段製程的FinFET、後段製程的銅雙鑲嵌製程,以及中段製程的傳統接點方案。愛美科的兩位計畫主持人於本文呈現了下一代的前、中、後段製程技術,以及其他能夠進一步推動未來的創新選擇,開出一條邁向1nm世代的可能途徑。

(本文由愛美科授權刊登;作者Zsolt Tokei1、Naoto Horiguchi2為愛美科1奈米互連導線研究計畫主持人、2邏輯CMOS微縮研究計畫主持人;編譯/吳雅婷

)

**刊頭圖(source:imec-int.com)