就特性上來說,FO-WLP/PLP是一種具有比覆晶封裝具有更好電氣特性的封裝觀念技術,並且在面對晶片薄化要求時,也具有較小熱變形的特性。從大約五年前開始,逐漸擴展應用在RF,功率放大器,基頻等等的晶片產品上。更進一步的,從今年開始,由於出色的電氣特性和佈線密度,FO-WLP/PLP更被應用在自動駕駛必或缺的雷達半導體上。

與常規的覆晶封裝相比,雖然FO-WLP/PLP能夠達到更高性能和更薄的晶片體積,但是因為來自於FO-WLP/PLP的製程良率和材料等等的相關問題,也大程度的影響了FO-WLP/PLP生產成本。

當然,在一項新的生產技術在被導入時,常常會面臨著許多的課題需要被解決,包括了生產設備、材料、製程手法等。當然,今天的備受注目的FO-WLP/PLP也是存在著這些無法避免的挑戰。

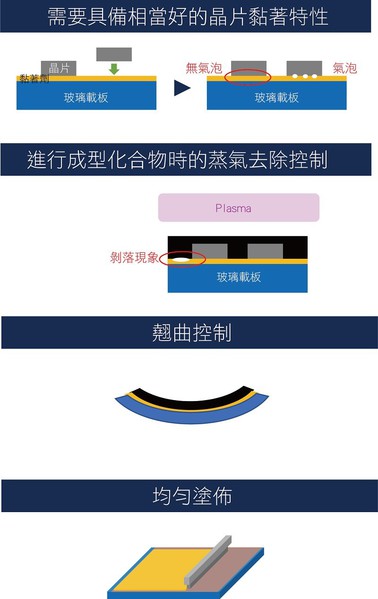

以目前的技術材料限制下,就大方向而言FO-WLP/PLP這個新的技術急需要面對幾項問題跟挑戰。包括了,黏著劑需要具備相當好的晶片黏著特性、進行成型化合物時的蒸氣去除控制、翹曲控制,以及針對面板級製程的均勻塗布與Debonding(圖一)。

| 圖一 : FO-WLP/PLP急需要面對的問題跟挑戰(參考資料:TOK、智動化整理繪製) |

|

第一、在進行晶片固定製程時,黏著劑扮演著非常重要的角色,是否挑選了特性相當優秀黏著劑的話,將會直接影響產品的良率,也就是說成本是否能夠降低的一大關鍵因素。

黏著劑的基本作用是能夠讓晶片可以在基板上黏著好。由於在進行晶片固定時,會對晶片施加一定程度的壓力,讓晶片能夠固定在預定的位置上,如果黏著劑不具備較佳的黏著性,會在晶片與基板之間產生空隙,使得空氣跑進這些空隙之中,形成所謂的氣泡。因此,選擇黏著劑的第一要件就是要不容易在晶片與基板之間產生氣泡。

第二、再來就是需要一個與黏著劑搭配最適合的molding製程,因為當晶片固定基板時,molding製程的特性是高溫又高壓,如果黏著劑在高壓、高溫之下,會出現黏著效果不佳的情況下時,就會使得晶片出現位移,而造成失敗的現象,因此,必須要高壓高溫之下,黏著劑能夠把晶片固定的非常牢固,這時molding就是一個非常重要的技術。

第三、就是要能控制所謂的蒸氣發生,當在進行molding的製程後,是很容易會出現蒸氣,因為裡面會有一些水分子造成蒸氣,而這些由水分子產生的蒸氣,會讓晶片與玻璃層之間產生剝離的情況,所以蒸氣的控制是非常的重要。

最後,是翹曲的控制(Warpage control),尤其是在面臨進行Fan Out面板級製程時,會經常遇到所謂捲翹的問題,面板大概會產生在2~3mm的翹曲,而這樣的彎曲程度會讓基板與晶片出現10mm左右的間距。因此,這時就必須透過專用的設備與技術,來對基板進行翹曲的控制。

需要相當好的晶片黏著特性

導入Fan Out製程時到底要怎麼樣來選擇這個黏著劑的特性,就是說要能夠容易進行黏著。當然黏著力是最重要的條件,除此之外,還必須有耐熱的能力與容易被完全清除,而且更需要能適用在EMC(環氧成型化合物;Epoxy Molding Compound)mold這個製程之中。

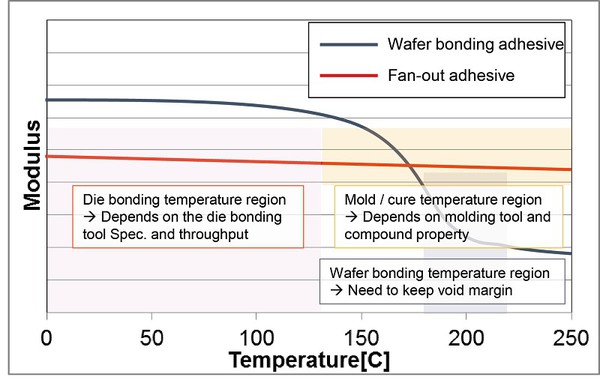

圖二是一項對於不同黏著劑在溫度與模數(Modulus)的比較結果。在圖中,橫座標代表的是溫度,而直座標則是Modulus,在這裡Modulus所代表的是固定能力,Modulus越高的話,固定能力就愈強,而Modulus愈低便是愈柔軟。

| 圖二 : 黏著劑在溫度與模數(Modulus)的比較結果。(資料來源:TOK) |

|

越牢固越下面,它就越鬆。黑色這個曲線代表的是在進行Wafer bonding常用的黏著劑,而紅線則是Fan Out製程所專用的黏著劑。

從圖表中可以看到,Wafer bonding常用的黏著劑,在溫度200度以內時,這個黏著劑的黏著能力是可以將晶片黏著的相當穩當,但當溫度高於200度時,就開始軟化,而軟化也就代表固定效果變差。也就是說,當進行晶片與玻璃基板Wafer bonding製程時的溫度,必須要在200度以下的溫度,才具備高度的黏著可靠度。

而代表Fan Out製程所專用黏著劑的紅色這條線,雖然它的特性在較低溫時,也是較柔軟,但是製程溫度持續增加下,即便是超過了200度,還是可以維持在一定範圍的黏著能力值,因此相當容易能夠依照這個特性來調整相關的製程。

一般來說,Fan Out製程技術下,當在進行晶片bonding階段的溫度大多是100度以下,不過當製程來到molding,也就是晶片固定,這時候的溫度就會升高到180度左右,如果這時黏著劑的耐高溫能力不足時,就會出現前述晶片位移的情況而導致失敗。也就是說在進行晶片molding的時候,黏著劑必須要在高溫維持可以黏著相當牢固的這樣一個特性。

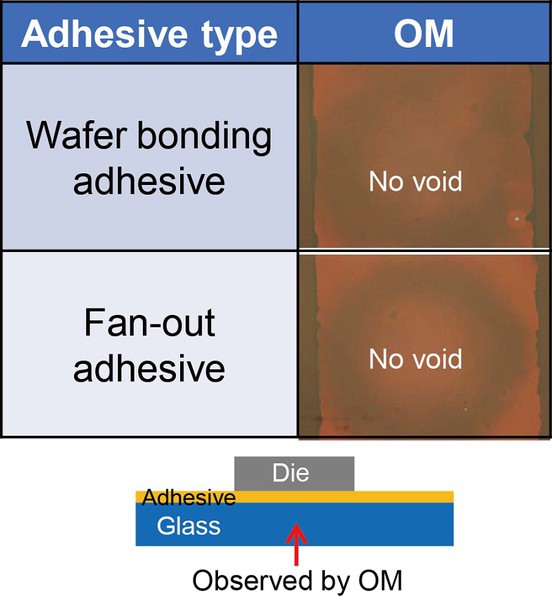

圖三和圖四是日本東京應化工業在Die bonding跟molding的部份,做一個黏著劑的一個比較模擬驗證結果。

測試的條件是,在玻璃基板上,分別塗佈了5μm的Wafer bonding與Fan Out製程用的粘著劑,而晶片的面積是5mm X 5mm。之後在80度的溫度下進行bonding。

首先從正面的俯視照面看下去,可以發現圖三中,無論是使用Wafer bonding或Fan Out製程用的粘著劑,都是沒有氣泡的,也就是說沒有空洞。

| 圖三 : 粘著劑塗佈後,正面的俯視照面。(資料來源:TOK) |

|

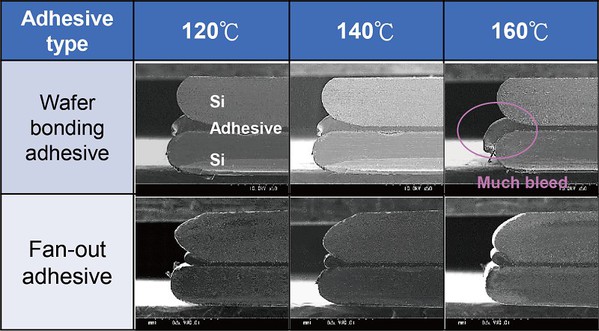

但是,當進行molding製程時,測試的條件是塗佈了50μm的黏著劑,但是因為東京應化工業並沒有molding的設備,這個測試是工程師利用上下都是矽膠來代替晶片與玻璃基板。測試的溫度分別是攝氏120度、140度跟160度。

當進行測試時,就會發現到當溫度升高時,圖四的雙方會有相當明顯的變化,尤其是在邊緣的部分。在120度和140度時,雖然邊緣的變化其實不大。但是當溫度已經來到160度的時候,可以發現矽膠的邊緣會有黏著劑一點點溶解所產生凸出的一個變化。

| 圖四 : 當溫度升高時,雙方會有相當明顯的變化。(資料來源:TOK) |

|

所以經由這個驗證可以知道,如果使用Wafer bonding黏著劑在進行molding製程時,在高溫的情況下會有Die bond的位移,如果是使用專為Fan Out所開發出來黏著劑,可以看到它在各種溫度,尤其是在高溫的情況下,是不會有任何的變化。

也就是說,在進行molding製程時選擇針對Fan Out專屬開發的黏著劑是非常重要的。

蒸氣的去除控制

選擇不適當的黏著劑除了在molding階段會造成晶片位移之外,還有很大的可能性會出現蒸氣。大家都能夠了解,如果不採取有效解決方案的話,就照這樣molding下去,其實會產生非常嚴重的蒸氣問題。因此,接著來討論Degas的挑戰,如何在molding這個製程下進行有效的蒸氣控制。

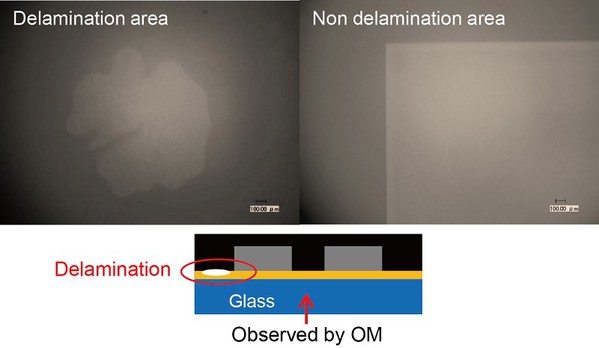

首先,先了解一下蒸氣會產生什麼問題。當把晶片置放上去之後,緊接著就會開始進行molding來將晶片固定,如果這時在晶片與基板之間產生空氣的話,不僅黏著效果會不好,甚至會有剝落的問題。這是因為mold compound的一個特性就是很容易吸濕,然後吸濕就會產生蒸氣,而蒸氣就會導致黏著剝落。

圖五是蒸氣的問題出現在molding時的結果。左邊的照片可以看出來出現很嚴重剝落的情況,而右邊則是沒有剝落的完全正常狀態。

| 圖五 : 在molding時出現蒸氣的問題。(資料來源:TOK) |

|

因為有蒸氣而產生的剝離現象,要怎麼樣去解決這個問題,主要來講可以有3個方法。

第一個方式,是讓黏著這個塗層非常穩定,固定的非常牢固。如果蒸氣很強的情況下,可以因為黏著劑本身非常的牢固,使得因為蒸氣所產生的影響會大幅降低。第二是改良mold compound,讓蒸氣量降低,但在mold compound這個部份降低蒸氣量其實是很難的,有技術上的困難性,目前還看不出來有比較好的方式。

第三是冷卻處理,因為在排氣之後蒸氣量會降低,所以在進行mold compound之前先做冷卻處理,可以有效減少蒸氣所帶來的影響。不過,這個方式大多業者都不太願意採用,因為會影響到製程,整個時間跟效率是會對成本帶來巨大的影響,所以這樣的方式不太容易被接受。

關注熱膨脹係數來降低基板的翹曲

另外,對於FO面板級的製程技術而言,翹曲的控制也是影響良率的一個關鍵課題。

圖六與圖七是翹曲(Warpage)控制的案例。在這兩個案例顯示了熱膨脹係數(CTE)對於翹曲的影響。

在Wafer bonding下,把晶圓固定之後,可以看到矽晶圓的CTE大約是3 ppm,而玻璃基板的熱膨脹係數一樣是3 ppm,這代表著不太存在因為熱膨脹係數所帶來的影響,因此在Warpage影響中,曲線幾乎是呈現水平的。

但另一方面,環氧成型化合物 (Epoxy Molding Compound;EMC)的mold compound大概是10 ppm左右,所以貼合在3ppm的這個玻璃上面,它的翹曲度就會相對變得很大。這個就是所謂熱膨脹係數的誤差率,也就是3 ppm跟10 ppm之間的落差,落差越大所造成的翹曲率就越大。

因此需要去選擇玻璃材質熱膨脹係數的值,只要拿捏恰當,翹曲率就可以被控制得很好。這是單純針對EMC的這個製程,在玻璃基板所顯示的一個結果。

但是會影響翹曲並非只有玻璃基板材質的熱膨脹係數,因為在製程裡面還會有RLD跟D晶片,所以再加上去又出現更多不同的組合結果。所以,降低翹曲率從熱膨脹係數做一個調整可以達到有效的改變來達到降低的目的,另外,也可以利用Fan Out 面板級專用設備來改善翹曲的問題。

對面板級製程的均勻塗布與Debonding

黏著劑的塗佈對於Fan Out 面板級也是一項相當程度的考驗。一般來說,黏著劑在晶圓級的塗布方式和面板級的塗佈方式有著結構性的不同。

從圖八可以看出來,晶圓級是透過Spin的方式來進行coating,而面板級則是採用Slit 的方式coating。

| 圖八 : 進行Coating製程時,晶圓級是透過Spin的方式,而面板級則是採用Slit 的方式。(資料來源:TOK) |

|

其實,對於LCD、FPD等平面顯示器製程中.本來就有Slit coating這樣的一個技術,但是同樣的設備卻並沒有辦法完全被套用在Fan Out製程技術裡。主要有3個原因。

首先,塗布的時候沒有辦法均一,對於Fan Out面板級來說,coating之後需要有均一性平整性。

以FPD來講,它只要15 mm裡面塗滿就可以了,但是面板級它就更嚴謹,只能從邊緣開始算5到6個mm,大概3分之1不到,以厚度來講,必須要很精準在5mm裡,而且要均勻的塗滿、塗平整,這是非常難的。

再來是氣泡的問題,面板級因為比較厚,所以需要的塗層也比較厚,因此黏著劑濃度比較高、比較黏稠,所以中間就容易產生氣泡。因此必須要去除這些氣泡,如果利用一般FPD的技術,來把這個氣泡脫除掉是很困難的,這時就必須在PUMP這個部分做改變,來進行改良。

再來就是先前提到的捲曲控制,因為只有10 mm那麼大。如果是產生這麼大的翹曲的話,就需要藉由設備讓基板平整,這是非常重要的,因為如果面板出現這麼大的翹曲,是完全無法進行Slit coating,使得在良率上會出現很大的問題,所以很重要的就是進行Fan Out時要去控制捲曲度。另外還有debonding和Transfer bonder的部份。

以面板及製程來講,必須要能夠控制它的壓力,越大的面積,就必須要均勻的去控制壓力,未來市場的需求是650mm乘以650mm這麼大的面板的需求,所以這個部份的控制跟合併技術的開發跟設備的需求,都非常的重要,不僅可以防止氣泡出現,還可以達到容易脫模。

目前大多是用雷射去脫模,所以處理時間就會變成是一個關鍵。相對於一般12吋的晶圓來講,面板是非常的大,所以雷射反應的處理時間就會變得更長。

另外,晶圓脫模之後的一個關鍵是handling。在Wafer製程的時候,是採用Dicing tape來做handling,但是在面板的部份是沒有Dicing tape,所以脫除之後面板的handling就很重要。