智慧手機的問世,給半導體產業設定了一個明確的目標,就是晶片體積只能愈來愈小,同時功能還要愈來愈強大。接著IoT來了,更多元的想像又被加了上去,晶片的設計和製造至此來到一個新的轉折。

於是,異質整合(Heterogeneous Integration)的概念,就砰然降臨到了半導體的舞台上。

SoC催生異質整合思維 SiP帶來實作成果

要談異質整合之前,就先得知道同質(Homogeneous)整合。言簡意賅的一句,就是相同功能的相加。最最經典的例子,就是CPU的多核心設計,不管是大核加小核,或者四核和八核,都是同樣的原則。

但在體積尺寸限制的前提下,同質整合的設計必定要往更小的製程發展,因此也有一說,同質整合和摩爾定律是互為因果。

只不過體積終究只是終端需求的其中一項,更困難的是把其他的功能也加在一起。因此系統單晶片(System on a Chip,SoC)的概念就誕生了,不僅要小體積,同時要具備其他的功能,最好把整個系統都做在一顆晶片裏頭。完整的體現就是如智慧手機這類型的產品,輕輕薄薄的一台,卻強過了過往的任何一台PC。

什麼是異質整合,就是把分開製造的元件進行更高層級的組裝,而這個集合將可以提供更強的功能性,同時也改善運作的品質。

有了SoC的設計思維,整合異質的想法也就慢慢誕生了。但由於SoC的設計和生產皆不易,尤其到了更先進的奈米製程之後,一顆SoC的開發費用動輒達到數十億元,一般中小型的公司根本難以負擔,因此轉用封裝的方式來達成整合的效果,則是更經濟和務實的做法,因此系統級封裝(System in a Package,SiP)便逐漸吸引了更多的目光。

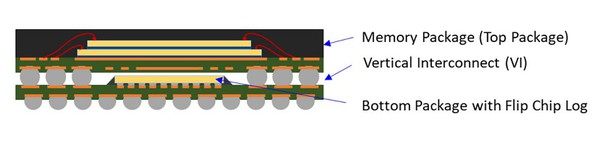

而隨著製程與設計架構的持續發展,傳統的2D平面設計逐漸不敷使用,立體式的製程架構開始被提出,於是晶片製造商便轉往3D IC和3D封裝的技術研發,而這種新型態的3D晶片製程技術更為異質整合帶來了更多的可能性。

成立聚焦團隊 具體描繪異質整合發展藍圖

因此,國際半導體技術發展藍圖組織(International Technology Roadmap for Semiconductors,ITRS)在2014年成立了異質整合的聚焦團隊,並在隔年於半導體產業(SIA)的認可之下,與IEEE的電子封裝社群(EPS)簽屬了合作備忘錄(MOU),確保異質整合可以永續的發展。至此,異質整合正式成為半導體產業的發展方針。

在2015年的半導體2.0國際技術藍圖裡,異質整合首次有了明確的說明,在其將近100頁的內容裡完整的描述了異質整合所涉及的種種面向。

| 圖一 : ITRS在2015年於半導體產業(SIA)的認可之下,與IEEE的電子封裝社群(EPS)簽屬了合作備忘錄(MOU),異質整合正式成為半導體產業的發展方針。圖為其組織的識別。(source: IEEE) |

|

什麼是異質整合,ITRS解釋,就是把分開製造的元件進行更高層級的組裝,而這個集合將可以提供更強的功能性,同時也改善運作的品質。而這裡所稱的元件,應該要包含個別的裸晶(die)、MEMS裝置、被動元件、組成的封裝,或者被整合至單一封裝裡的子系統。

而所謂的運行性能,也應該要採用最廣義的思考,例如擁有者的系統成本。

ITRS指出,傳統的COMS製程已經接近極限,而持續的產業成長和持續縮減的每單位功能成本,將需要新的裝置型態、新的封裝架構和新的材料來因應。尤其當摩爾定律可能走到終點的時候,透過在封裝上創新的異質整合和三維架構技術所達到的功能多樣化,必須適時接棒而起。

3D封裝與有效率的供應鏈是關鍵

而採用封裝製程的SiP將會是最關鍵的技術,它是平衡性能多樣化與成本的最佳解決方案。因應這個新架構,包含印刷電路、更薄的晶圓、以及主動/被動的嵌入式裝置都會因此而興起,然後用在封裝的生產設備和製程材料也會有快速的變化,以滿足新的架構需求。

未來15年內,異質整合的佈局會著重在組裝(assembly)和封裝(packaging)、測試、與導線互連(interconnection)技術。而SiP架構將是異質整合技術的主要貢獻。

ITRS也提到,對於製程微縮成本最重要的事,是建立並維持有效率的供應鏈,而這需要協調多個IDM廠、晶圓代工廠和測試業者。而一個有效率的供應鏈也將自然地專注在各種降低成本和形成標準的活動上,以維持競爭力。

至少在未來的15年內,異質整合的佈局會著重在組裝(assembly)和封裝(packaging)、測試、與導線互連(interconnection)技術。而落實功能多樣性與系統層級整合的SiP架構將是異質整合技術的主要貢獻。

封裝是晶片進入終端裝置的最後一道流程,它要提供電子和光訊號的輸入輸出,電源連接和電壓控制,它也要提供散熱和實體的保護。而正興起的IoT和雲端數位應用趨勢,以及趨緩的CMOS摩爾定,將會從各方面給封裝技術帶來新的需求。而最重要的技術,就是複雜的3D系統封裝架構。

| 圖二 : 封裝是晶片進入終端裝置的最後一道流程。而正興起的IoT和雲端數位應用趨勢,將會從各方面給封裝技術帶來新的需求。(source: IEEE) |

|

ITRS並提出了四個主要的應用領域,分別是高性能運算(HPC)、高速低延遲通訊、物聯網、消費性電子。但到了2019年,更多的應用領域被加到了研討的項目中,包含汽車、醫療與穿戴式裝置、國防與航太等。

當然,為了務實的推動異質整合在產業界的發展,IEEE EPS和SEMI也成立了相關的委員會並設定執掌,讓各項工作更有所本。其中全球諮詢委員會(Global Advisory Council)是最為知名的一個,期主要的目標之一就是確保異質整合的價值主張能落實在政府、產業、學界與研究中心等,同時也作為溝通和舉辦會議的聯繫介面。

鈺創科技盧超群 率台灣業者進軍新領域

目前的主要成員包含:SEMI的總裁與執行長Ajit Manocha、鈺創董事長盧超群、英特爾副總裁與封測部門總經理Babak Sabi,以及Fraunhofer董事長Hubert Lakner。

值得一提的是,台灣的鈺創科技董事長盧超群不僅是異質整合的倡導者,更是一個身體力行的實作者。他除了擔任了台灣人工智慧晶片聯盟的會長,實際推動產業界把AI晶片落實在異質整合的應用,他所創辦的鈺創科技也在近年研發出新一代的RPC DRAM記憶體架構,透過在不影響效能且滿足業界標準的前提下,大幅縮減了針腳通道數,讓超微小化成為可能。

| 圖三 : 鈺創科技的RPC DRAM,為記憶體的整合應用開創新的視野。 |

|

盧超群指出,他所發明的新型記憶體能輕易的被整合至各式的嵌入式設計中,同時鈺創也提供KGD(Known good die)的規格,以便被運用在SiP和其他的晶片整合技術中,進一步實現更高性能且多工的終端產品。

他表示,異質整合是未來20~30年半導體發展的重要方向,透過把一個系統用不同晶片整合在一起,產生可用於不同領域的應用,像是把感測或者運算的元件整合到生醫領域中,產生能治療癌症的裝置,這就是異質整合其中一個實際的應用案例。

結語

日前,在2019的Hot Chips論壇上,英特爾也再次展示了首款使用Foveros 3D封裝技術的Lakefield PC處理器。該處理器就是英特爾首次使用異質整合架構的處理平台,透過整合了CPU、GUP與記憶體元件等,在一顆晶片內實現了市場罕見的功能與性能。

英特爾新晶片的問世,將會是一個序曲,接下來可見到越來越多的廠商發表類似架構的產品。而隨著技術與市場的成熟,異質整合的時代大戲,也就會慢慢登場了。