今年全球第二大國際半導體展會SEMICON Taiwan於9月18~20日登場,此次展出分為五大區:扇出型封裝專區、測試專區、光電半導體專區、化合物半導體專區和異質整合創新技術館。其中,異質整合(heterogeneous integration,HI)被視為引領下世代半導體的關鍵技術,為半導體發展提供微縮電晶體之外的創新思維。

自2015年起,異質整合發展藍圖(Heterogeneous Integration Roadmap,HIR)開始成形,接續國際半導體技術發展藍圖(International Technology Roadmap for Semiconductors,ITRS)引領半導體至2031年甚至更往後的發展。

半導體的發展和物理特性有密不可分的關係。半導體的本質就和導電性有關,再談論到半導體製程,從石英砂純化出冶金級的矽,到製作出晶圓、晶片並封裝,這套流程便是運用純度、密度、粒度、導熱性和延展性等物理性,建構出得以進行運算、記憶和能量轉換的科技產品。

而後,摩爾定律的問世引領著半導體產業逐步挑戰物理極限。今年四月台積電才宣布全球首座5奈米晶圓廠完工,再次邁進摩爾定律的下一個技術節點。這個新聞著實令人振奮,然而近幾年的技術節點進展並非如過往順利,各科技大廠的研發時距拉長,引發市場對摩爾定律有效性的擔憂,其中很大的因素在於嚴苛的物理極限帶來的成本增加。

是的,半導體之所以壯大成一產業,除了在工藝研究上帶來革命性的新技術,更重要的是其應用廣泛性。也就是說,技術開發完成後要能夠量產,之後才有機會應用在各類3C、醫療、車用、航太等科技產品。當電晶體縮小至物理極限—或者說是符合經濟效益的製造成本最大值時,為摩爾定律另尋挑戰物理特性的製程也就應運而生,而那就是異質整合。

甚至可以說,異質整合是助力半導體產業脫胎換骨的靈丹妙藥,以結合具備不同材料特性和物理需求的功能區塊,打造高整合、低功耗又小巧的晶片設計。

綜觀未來半導體的應用,以高效率運算(HPC)、低功耗和小型化為目標,因此晶片上的I/O介面接點數量、散熱效果和封裝體積便是後續技術節點的發展重點,加上先前所說製造成本的考量,這些要素可以是各半導體大廠的痛點,也可以是賣點,將決定下一代半導體的新樣貌。

新樣貌一:追求小型化 醫療穿戴裝置的多功能區塊整合

醫療領域在半導體應用藍圖中的重要性與日俱增,除了已開發國家普遍的高齡化問題之外,現代人時常面臨的諸如高血壓、心臟病等慢性病,以及亟需長期監測的疾病或症狀,像是癲癇、失眠等,在在反應醫療穿戴裝置的需求正在增長。

一方面,為了在一定時間中更準確監測病患身體狀態,同時也能方便病患配戴,穿戴式裝置對結合邏輯、感測、記憶和電源元件的需求轉為強勁,以智慧型電子裝置型態發展,未來這些裝置將集結更多不同功能元件至更小的晶片上,並以低功耗運作。

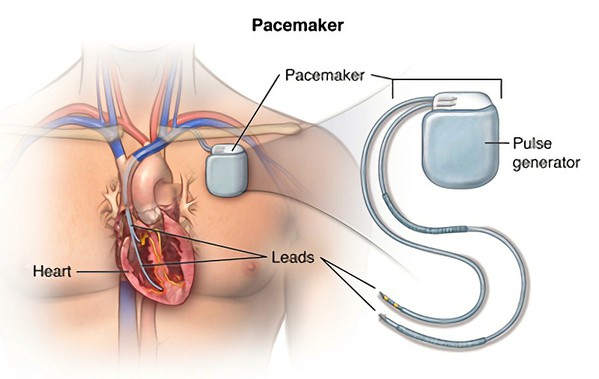

以心臟調節器為例,它可以感測並記錄病患心律,並在心跳過慢或休止時適時釋放適當電流,以維持病患正常心跳。此裝置包含兩大部分:起搏器(pulse generator)和電極導線(lead)。起搏器包含電源、記憶和邏輯元件,負責記錄心律資料及調節心跳,而電極導線接收心跳的訊號,並在病患心律異常時傳輸電流,以刺激該心臟回復至正常心律。

| 圖一 : 心臟調節器包含兩大部分:起搏器(pulse generator)和電極導線(lead)。(source:hopkinsmedicine.org) |

|

除了心臟調節器,心臟去顫器、植入式助聽器、人工電子耳和人工視網膜等也是常見的植入式醫療穿戴式裝置。其他醫療穿戴式裝置則包括健康監測設備—用來監測疲勞、壓力和傷口復原狀況等,以及醫學成像設備—像是X光、磁振造影(MRI)、電腦斷層攝影(CT)和超音波等,還有診斷系統—例如健康手環和智慧型手錶。

從這些特定應用的穿戴裝置可以發現,醫療穿戴裝置對感測元件的需求特別明顯,依感測功能又分為加速器、迴轉儀、地磁儀和全球衛星導航系統(Global Navigation Satellite System,GNSS)等運動感測元件,以及偵測心跳、血氧或體溫的元件,其他元件則包含電力、射頻或化學感測元件。

系統級的整合對穿戴式裝置的性能有決定性的影響,也就是說,異質整合技術能決定整合的功能多樣性、噪音、電磁干擾遮蔽(EMI shielding)和功耗等面向的表現。而要整合不同功能區塊,常見的異質整合技術是透過新興封裝技術來達成,例如:矽穿孔(TSV)和矽中介層、覆晶封裝(flip chip)、扇出型晶圓級封裝(FOWLP)等。

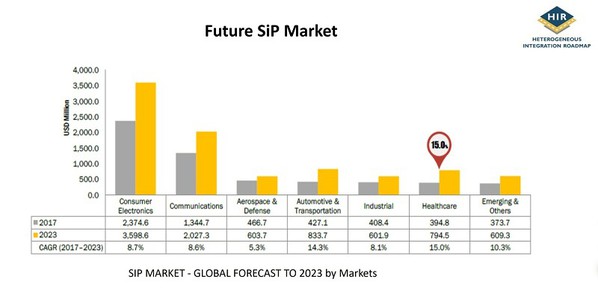

目前,由於各電子元件的封裝尺寸大小不一,穿戴式裝置多半採用系統級封裝(SiP)來結合諸如微控制器、記憶體、天線或微機電(MEMS)元件。今年國際電子元器件技術會議(IEEE-ECTC)其中一場異質整合研討會(HIR Workshop)便在探討系統級封裝未來的市場,其中以醫療保健領域的發展潛力最顯著,預估至2023年其年複合成長率(CAGR)可高達15%。

| 圖二 : 系統級封裝未來以醫療保健領域的發展潛力最顯著,其年複合成長率(CAGR)可能高達15%。(source:ieee.org) |

|

智慧型手錶是最有潛力發展成新興的消費性醫療裝置之一。以Apple Watch Series 2為例,其堆疊三個晶片尺寸封裝(CSP),包括控制器、慣性感測器,以及結合雙核微處理器和DRAM的系統級封裝晶片。

透過新興封裝技術,醫療穿戴裝置得以實現裝置小型化。目前醫療電子產品的封裝趨勢為小型化,然而,醫療電子產品追求的功能各不相同,大部分廠商都不願意提供客製化的解決方案,因為相較於智慧型手機等行動裝置,醫療裝置的產量不豐,因此降低產品的單位成本變成這類裝置的發展重點。

新樣貌二:面對高複雜度 車聯網的全方位串連系統

和醫療穿戴裝置追求小型化不同,汽車的發展以高自動化、安全性和通訊(communications)為目標。從個別車輛的獨立系統—像是先進駕駛輔助系統(ADAS),到連結車輛、交通號誌燈和行動裝置的智慧交通互聯系統,半導體在汽車領域的發展聲勢看漲。而異質整合便扮演著提供互聯(connectivity)、感測(包含雷達、光達、超音波和影像感測器等)和先進處理器解決方案的角色。

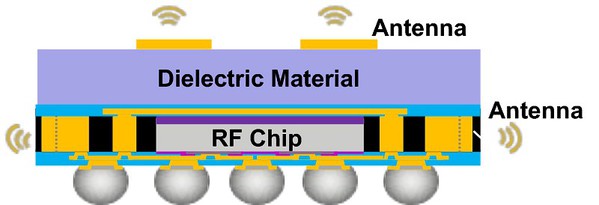

在互聯方面,未來自駕車能透過天線封裝(Antenna in Package,AiP)達成5G毫米波的高頻傳輸技術。以台積電的天線封裝技術為例,其採用整合扇出型封裝(InFo),晶片上有射頻晶片和佈建在重分佈層(RDL)的天線,該射頻晶片和重分佈層不需凸塊(bump)和錫球(solder ball)就能內連。

| 圖三 : 台積電的天線封裝技術採用整合扇出型封裝(InFo),晶片上的射頻晶片和重分佈層不需凸塊(bump)和錫球(solder ball)就能內連。(source:tsmc.com) |

|

天線封裝技術便是未來異質整合的重點應用之一,利用晶片堆疊,或者說是2.5D甚至3D的封裝技術,連接晶片和天線,並提升兩者的整合度。而台積電採用的做法有別於其他槽孔耦合(slot-coupled)的天線架構,將饋入線(feeding line)置於封裝底層的重分佈層,並將之與封裝頂層的平板天線(patch antenna)耦合。

除了支援互聯需求,異質整合技術在車聯網的運算處理技術上亦有集大成而引發革命性能突破的潛能。車用CPU和GPU等處理器逐漸自以14nm推進至7nm的鰭式場效電晶體(FinFET)製成,而為了建構更有效率的ADAS系統,越來越多晶片採用人工智慧技術,以因應圖像處理和處理器內儲/讀取數據所帶來的高速傳輸需求。

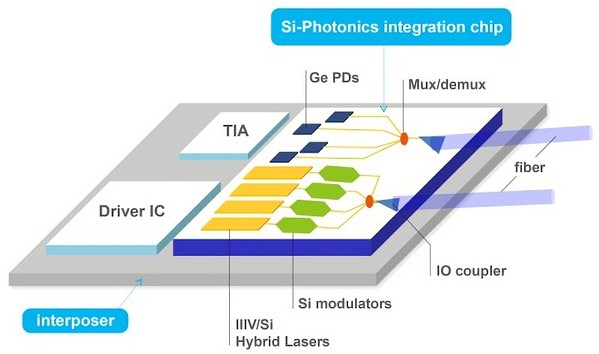

為了實現高速傳輸,除了持續微縮電晶體及採用系統級封裝以提高I/O數量和縮短間隙(pitch)外,矽光子技術(silicon photonics)是另一個富前瞻性的解決方案,近年來備受重視,其原理為以光訊號代替電訊號來傳輸資料。倘若光電整合技術成熟,將能大幅提升運算和傳輸效率。

| 圖四 : 矽光子技術(silicon photonics)以光訊號代替電訊號來傳輸資料,透過光電整合技術,將能大幅提升運算和傳輸效率。(source:itri.org) |

|

然而,半導體目前的主要材料矽(Si)自體不發光,如果要以光訊號傳輸,晶片上需嵌入光源,而光電的異質整合又是另一大哉問。此外,高速傳輸的另一挑戰是降低大數據運算的錯誤率,應用在自駕車領域上,則和路上安全有絕對關係。為此,高速傳輸的製程技術和創新材料開發成為半導體在汽車領域發展的關鍵。

在汽車的感測功能方面,感測融合技術(sensor fusion)的應用會更廣泛,由於平面交通的路況複雜度極高,單一感測器所能獲取的訊號有限,透過將不同感測元件廣泛互聯,運算複雜數據的處理器能整合更全面的路況資料,做出更精確的判斷。而就單一感測元件而言,廣域感測範圍的需求逐漸成長,在晶片設計上,基板將佈建更密集的矽中介層,接腳間距(ball pitch)也會從現在的7mm再微縮。

新樣貌三:邁向高速運算 資料中心的邏輯對記憶體整合

以宏觀的角度看異質整合,它帶給半導體未來發展無限想像。「異質」可以指不同材料(材質),也可以是不同功能(性質),不論是整合不同材質或性質,其技術難度皆大不相同,這也代表要建構完整的異質整合發展藍圖,僅提出單一解決方案是不可能的。

針對今年SEMICON Taiwan展會,Intel副總裁Koushik Banerjee便表示:「到目前為止,異質整合還聚焦於高頻寬記憶體與處理器的整合,我相信未來新需求將持續出現,並驅動異質整合技術進步。」

這種邏輯對記憶體(包含DRAM、SRAM、NVRAM)的異質整合將建立密集的內連導線(interconnection)。今年國際電子元器件技術會議(IEEE-ECTC)便訂定目標,未來五年邏輯對記憶體的晶片每秒將支援4000個通道(256GB)的數據量,未來十年則能支援每秒4000-8000個通道(超過512GB),實現超高效率運算。

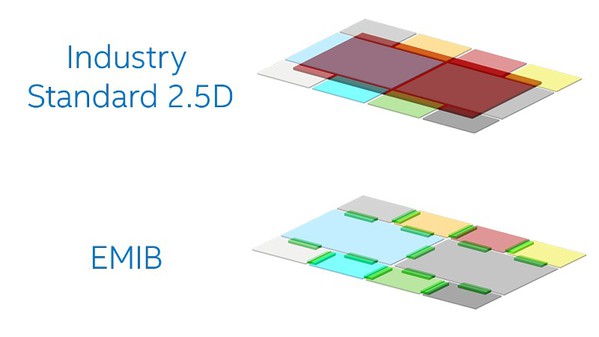

其採用的封裝技術囊括層疊封裝(PoP,Package on Package)、2.5D和3D封裝及其它創新垂直堆疊技術。舉例而言,英特爾日前便在SEMICON West會議上發表了嵌入式多晶片互連橋接技術(EMIB,Embedded Multi-Die Interconnect Bridge),以作為連接多個異質晶片的創新解決方案。和2.5D封裝解決方案不同,英特爾的EMIB技術不採用中介層和矽穿孔,而是在待整合的異質晶片間搭建橋接(bridge),在高密度訊號傳輸的區塊使用微凸塊,在晶片到封裝的接地連接和電源則採用覆晶微凸塊。

| 圖五 : 英特爾的EMIB技術在不同的異質晶片間搭建橋接(bridge),而不採用中介層和矽穿孔。(source:intel.com) |

|

這項技術不僅能減少佈建矽中介層的面積,降低單位生產成本,也讓晶片設計多了靈活配置的彈性。而隨著異質整合的發展潛能在不同應用上展現,可以想見異質整合將在封裝領域佔得一大新天地。

**刊頭圖(source:darpa.mil)