雖然信號處理一般總是要用到數位訊號處理器,但是,很明顯的發展趨勢是選擇FPGA作為實現高性能、高精度信號處理的平臺。

對於很多這類應用,通常是最終選擇使用一片FPGA、帶有相關DSP處理器或者一組DSP處理器的FPGA。

一般認為可以採用C語言對DSP處理器進行程式設計,這樣可以實現非常簡單的開發流程,但是,當設計被劃分到多個DSP處理器上,或者在DSP處理器和FPGA之間進行設計時,這種優勢就會消失殆盡。實際情況是,一片DSP處理器不具備完成大部分基礎設施系統所需要的信號處理性能。

這就要求系統設計人員在使用多片DSP處理器和FPGA之間進行選擇。後一種選擇總是能夠實現較低的系統成本和功耗。

圖一顯示了這些基礎設施系統的一個共同點——性能需求超出了傳統可程式設計數位訊號處理器所具備的性能。

| 《圖一 不同的應用有不同的性能、精度、IP和工具需求》 |

|

這些系統還有不同的性能和精度要求,以及不同的設計和開發流程。

例如,視頻處理需要9至12位精度,一些高端設計需要12位色彩深度。這些設計通常在HDL設計流程中完成,越來越多的使用視頻和影像處理IP功能來加速開發流程。

另一方面,軍用雷達設計要求盡可能提高DSP性能以及浮點精度,以獲得最大動態範圍。很多這類設計在MATLAB和Simulink工具中建模,提供適用于FPGA體系結構的浮點功能。

當選擇FPGA時,系統設計人員必須瞭解FPGA矽片體系結構,選擇設計工具、IP、功能系統模組以及適用的參考設計,以便能夠迅速高效的完成演算法程式。本文介紹一些加速FPGA-DSP設計實現的典型DSP解決方案。

設置FPGA精度以滿足您的應用需求

選擇符合您的演算法程式精度要求的FPGA-DSP體系結構。應避免按照FPGA供應商提供的任意精度範圍來劃分演算法程式。

傳統上,FPGA體系結構具有固定精度DSP結構,要麼浪費寶貴的矽片資源,要麼把設計畫分到多個模組上,這樣降低了系統性能。例如,實現HD視頻處理應用時,系統一般只需要9x9乘法運算,而固定精度18x25 DSP體系結構就有些浪費了。浪費了一半的DSP模組。

或者,實現複數乘法器時,在高性能DSP系統電路板上實現用於快速傅裡葉變換(FFT)功能的通用構建模組,在很多情況下,需要級聯DSP模組才能支援18x25或者18x36複數乘法運算。需要確認DSP模組有足夠寬的級聯鏈和累加器寬度,通過專用佈線來實現級聯鏈。使用FPGA中的通用佈線會產生性能代價。或者,如果級聯匯流排/累加器不夠寬,您不得不在連接下一DSP模組前採用一個精度位。

有些設計人員會為部分設計實現浮點資料通路。這些功能需要24位或者更高的精度在一個精度格式中實現尾數乘法。

當選擇FPGA-DSP體系結構時,確定這一體系結構能夠支援多種精度範圍,有足夠寬的級聯匯流排,滿足系統精度要求(參見表一)。

(表一) 28nm DSP模組體系結構支援的精度模式

| 28nm一個‘精度可調D模組 |

| 三個獨立9x9 |

| 2個匯總模式18x18 |

| 兩個32位解析度的18x18 |

| 1個獨立模式18x25或者18x36 |

| 一個獨立模式27x27 |

最常在FPGA中實現的功能之一是有限衝擊回應(FIR)濾波器。非常重要的是,FPGA DSP模組體系結構能夠有效的支援高性能、多通道FIR濾波器的實現。Altera在設計28nm DSP體系結構的一些關鍵特性時,非常注重FIR濾波器設計,如表2所示。

(表二) 實現FIR濾波器設計的DSP體系結構特性

| 28nm“精度可調”DS模組 |

優點 |

| 內部係數寄存器 |

更高的fmax,更少的外部寄存器 |

| DSP模組中兩級加法器樹 |

DSP模組中的加法器樹,減少了外部邏輯 |

| 硬核預加器(18位和26位) |

一半的對稱FIR濾波器,乘法器數量減半 |

| 脈動FIR輸出寄存器 |

不需要外部寄存器,實現脈動FIR濾波器 |

出於行銷的目的,有的公司宣稱按動按鈕就能夠在硬體中全部實現MATLAB/Simulink設計。但是,他們沒有注意到,這需要對設計進行很大的改動才能滿足所有時序約束要求。應該採用“時序驅動”Simulink綜合引擎。

這一工具不但產生了原始結構的HDL,而且能夠非常直觀的增加流水線或者時分複用功能,因此,得到的HDL滿足了fMAX或者延時約束要求。

Altera的DSP Builder高級模組庫就是圍繞這些目的來設計實現的。該工具分析Simulink設計描述,為目標FPGA器件生成HDL和位元流,含有時序約束–fMAX或者延時。通過加入流水線寄存器以及適當的時分複用功能來自動完成這一工作,以滿足甚至超過要求的時序。

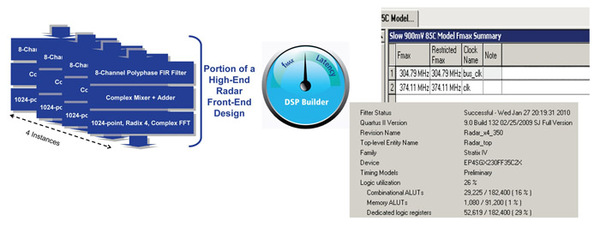

採用DSP Builder高級模組庫開發的大規模高性能軍用雷達設計不需要手動調整HDL就能夠達到時序收斂。

圖二顯示的例子中,50,000個邏輯單元(LE)的FPGA設計在350 Mhz達到時序收斂。雖然圖二中的設計實例只是一個雷達系統的前端,所實現的多相FIR濾波器、FFT和合成器等功能也經常用於很多高性能DSP設計中。

| 《圖二 50,000個邏輯單元(LE)的FPGA設計在350 Mhz達到時序收斂》 |

|

高清晰視頻處理——非常適合由FPGA來實現

對高清晰視頻的需求越來越大:

- ●視頻監控系統從標準清晰(SD)視頻發展到高清晰(HD),具有寬動態範圍(WDR)等功能,從而推動了高解析度視頻處理功能的需求。在很多工業圖像系統中,這一發展趨勢也非常明顯。

- ●廣播視頻系統逐步從1080p HD解析度發展到2K、4K和3D解析度,以滿足下一代影院和演播室需求。

- ●醫療成像系統解析度也越來越高,需要高性能信號處理功能。

視頻處理向1080p HD解析度發展,非常適合採用FPGA實現其功能。為FPGA開發視頻設計非常耗時,通過採用圖三所示的構建模組、標準視頻界面以及參考設計能夠顯著加速這一過程。

Altera的視頻設計工作臺包括18個視頻功能,支援流視頻界面標準,提供6個經過硬體驗證的參考設計,以及多種視頻開發套件。

採用視頻設計工作臺,您可以從已有的設計開始工作,在常見功能上重新使用經過預驗證的IP,例如,縮放、去隔行和合成等,加入到定制功能中,與從頭開發設計相比,在更短的時間內完成設計。

浮點精度:實現高性能DSP

在高性能DSP領域,浮點信號處理速度較慢,但的確是提高動態範圍的一種方法。在高級軍事STAP雷達、LTE通道卡的MIMO等化器,以及高性能計算等系統中都會有這種情況出現。最近的研究表明,2012年,FPGA DSP設計中浮點信號處理演算法的比例將從10%增長到20%。

浮點處理一般涉及到尾數乘法、尾數歸一化/去歸一化和指數加法。雖然指數加法/減法非常簡單,但是,尾數乘法和歸一化操作需要精度高於24位的乘法器。這可以通過級聯兩個定點DSP模組來實現,也可以配置一個高精度模式的精度可調DSP來實現。

實現浮點精度時,檢查DSP體系結構能否在一個DSP模組中支援浮點尾數乘法或者尾數歸一化操作。這不但能夠節省資源,而且還提高了性能(例如,更高的fMAX)。

FPGA供應商可以利用其體系結構,提供一組高效的高性能浮點構建模組IP內核,如圖四所示。

為浮點DSP應用選擇FPGA平臺時,應認真確定浮點運算的硬體效率以及能否使用構建模組浮點功能。針對浮點DSP實現進行了優化的FPGA DSP體系結構能夠提供更高的系統fMAX以及多種浮點功能,大幅度縮短了開發時間。

總結

FPGA供應商提供的DSP解決方案以及市場需要的解決方案都在隨時間的變化而不斷變化。在開始高性能DSP系統設計之前,應通過不同的晶片供應商來(針對產品及時面市)評估各種DSP解決方案。這不但能夠顯著縮短設計和開發時間,而且還體現了供應商對DSP市場的承諾。這對於支援和更新複雜系統非常關鍵。