晶圓級封裝(Wafer-Level Packag,WLP)是以晶圓(Wafer)為封裝處理的對象,而非如傳統的封裝係以單一晶片(Die)為加工的標的。因此,晶圓級封裝的製程已顛覆了傳統封裝流程,更引發半導體產業鏈之丕變。而晶圓級封裝則在進行切割前即已在晶圓上完成所有的封裝動作,故幾乎所有製作過程均在晶圓廠完成,而排除了封裝廠的傳統製程。

晶圓級封裝顛覆半導體製程

換言之,晶圓級封裝業已模糊了半導體IC在封裝及測試的地位,卻強化了晶圓廠的角色分量,亦即將封裝測試納入晶圓廠的製造體系之內,使封裝測試內化為晶圓廠的生產流程。一旦如此,對封裝及測試業的架構與生態將產生重大的影響,而就整體產業鏈中各別產業的定位將更趨模糊。再者,產業分工體系也將回歸整合態式,自80年代IDM解體以來,打破縱向產業的結合,創造出垂直分工的產業模式,但隨著成本、管銷及資源共享的發展下,整合的態勢卓然而起,逐漸地使垂直分工受到相當大的挑戰,故由晶圓級封裝的出現更可體現出業界為使成本最小化及製程最簡化的一大象徵。

晶圓級封裝相對於傳統的IC打線、導線架產業都出現革命性的轉變,晶圓級封裝等於是把許多封裝步驟都取代掉了,當一片晶圓從代工廠出來後,就直接在整片晶片上進行封裝製程,最後切割下來時,已經是一顆顆封裝好的IC成品,在時間及成本上都很經濟。

晶圓級封裝的介紹

晶圓級封裝(WLP)是延續CSP及與Flip-chip製程相通,而晶圓級封裝主要是要簡省後段製程,不再以W/B的晶片連結方式,而以晶圓廠的設備及製程以完成傳統封裝所能達到的工作。其構裝元件的外接訊號點皆屬內縮(Fan-in)的排列型式,構裝元件的尺寸與晶粒大小為1:1,承載基板為薄膜基板(Thin Flim Substrate),以類似覆晶的技術與晶粒連接,不需加入填膠製程,然後在晶粒面上以Area Array排列方式完成訊號接點(I/O)的重排。

(一)推動晶圓級封裝的幾個理由:

- 1.在晶圓層次及藉由晶圓廠之材料及設備以完成封裝之目的

- 2.使用標準之半導體製程以光罩等設備以因應設計上之改變並得以確保時效

- 3.排除因材料供應及設計變更而消耗之轉換成本

- 4.直接延續標準晶圓之製程可維持成本之掌控,無需再委外封裝

- 5.直接依客戶之需求而作調整,並同步完成製造及封裝之工作,可節省客戶另尋封裝所負擔之成本

- 6.測試方面可減少傳統製程需多次測試之缺點

(二)應用範圍:

- 1.Body size:<100 I/O 0.5~0.8mm Pitch

- 2.Applicable IC:

- Flash Memory

- DRAM(>64M)

- MCU

- Passive components

- Liner Ics

(三)結構及製程:

1.結構:

埠端重佈層(I/O Redistribution Layer)

應力緩衝層(Stress Buffer Layer)

護層(Passivation Layer)

2.製程:

薄膜沉積(Thin Film Deposition)

微影(Photolithography)

蝕刻(Etching)

電鍍(Plating)

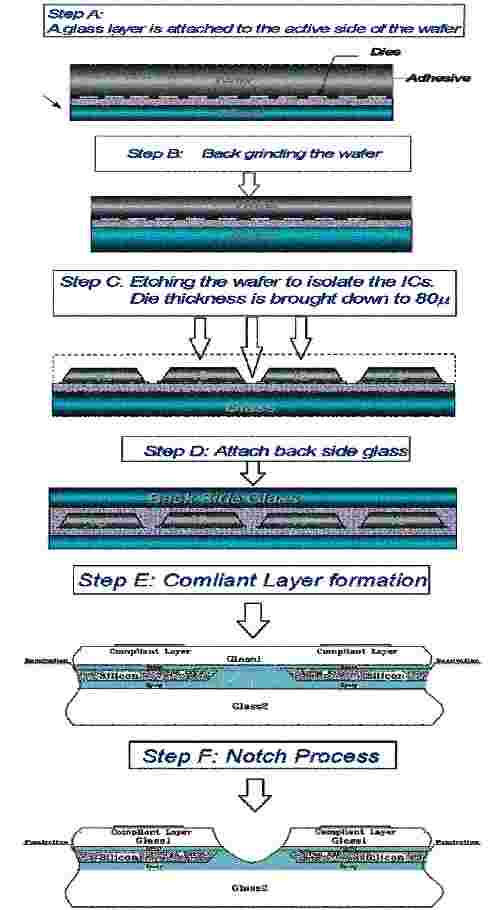

印刷(圖一)

| 《圖一 Wafer-Level Package Prpcess》 |

|

在製程上多屬晶圓廠的黃光製程,並非傳統封裝廠所熟知者,但相反地,卻與Flip-chip Bumping有其相通之處,故就此製程及經驗上而言,晶圓廠確實比傳統封裝廠進入障礙較低,而上述製程可視為IC全製程的一部分,則從晶圓製造經封裝測試後即交與客戶手中,而無需再透過封裝的程序加工。

(四)市場現況:

1.全球市場情境

現今市場可見的Wafer Level Package,除了單晶片外尚有多晶片(Multichip)的3D堆疊(Stacked)之封裝型態,在類型上可述之如(表一)。Wafer Level Package市場上現以CSP型態為主,在估量上則如(表二)。

2.國內市場情境

國內在Wafer Level Packag尚屬萌芽導入期,故在Solder Bump的供應上仍嫌不足,且需求尚不明顯,故國內封裝業界介入者不多,如眾晶引進Shell Case的Wafer Level CSP,但實際情形仍不明朗,但由最近無論晶圓廠或封裝廠皆逐步地朝Flip-Chip Technology發展。換言之,發展Flip-Chip Technology可謂進軍Wafer Level Packag的前置階段,可歸納如下:

日月光

封裝大廠日月光日前與美國凸塊(Bumping)製程專業公司FCT(Flip Chip Technologies)簽約,將移轉FCT專長的凸塊製程,計畫在明年第一季量產覆晶(Flip Chip)封裝技術。目前國內專門以凸塊製程為營業項目的公司有三家,分別為福葆、頎邦、及慎立科技(鴻海、聯電及矽豐所合資),但客戶群仍以液晶顯示器廠商為主。台積電也在評估是否要在晶圓廠內增設凸塊製程,預計今年之前會完成評估。日月光與FCT的策略聯盟,拉開了國內半導體封裝業者進軍覆晶領域的熱身運動,將來更可提供前來台灣下單晶圓代工的半導體業者,一套完整的構裝解決方案。

日月光這次選擇結盟的FCT公司,是美國已經開始接單量產的凸塊製程公司,其製程是以鋼版印刷的方式,在晶圓表面的I/O上長出金屬凸塊,這種鋼版製程有別於國內三家廠商以電鍍的方式長凸塊。據悉日月光已有數家客戶提出對覆晶技術及凸塊製程的需求,尤其在台積電與聯電等代工大廠逐漸走進0.18微米後,使用到覆晶技術的產品也越來越高。日月光預計在今年第三季開始引進設備,明年第一季提供客戶包括凸塊製程的覆晶封裝技術。

矽品

矽品在二年前就參與投資晶圓凸塊(Bumping)技術公司APTOS(在園區設廠名為慎立科技),在其中佔五%的股份。同時還投資了一家前任安南美國公司總經理所創立的ABPAC公司,金額有一千萬美元,佔這家公司股份的37%,進行覆晶式技術的開發,最近也派出矽品的團隊至美國移轉技術,並開始為客戶設計工程樣本。

覆晶式封裝適合於高I/O、高頻、高密度的IC,最先採用此封裝技術的應為繪圖晶片及晶片組,目前矽品為客戶展開設計的產品是繪圖晶片,其預測公元二千年時台灣廠商的晶片組產品對覆晶技術的需求會提高。此外,矽品還參與投資美國Artest公司,投資額四百萬美元,約佔30%的股份。Artest是邏輯及混合式訊號IC的測試廠,去年營收有四百萬美元,針對下一世代的晶圓級封裝,矽品去年初投資一百萬美元在美國波士頓的EPIC公司,已經向客戶交出工程樣本。

華治科技

華治科技亦積極介入先進封裝技術,如MCM、Flip-chip等技術以做為進入Wafer-level Packaging的準備。其他如福葆、頎邦及慎立亦從事晶圓凸塊的封裝技術。

3.小結

表二中雖然WLP的預估佔有比率在CSP之中仍屬微不足道,但長期來看,此種封裝技術(以Flip-chip Technology為連接晶片的製程),一則足以改變傳統晶圓廠及封裝廠間供需的關係,轉變為競爭的關係;二則對Design House及模組廠亦因流程的轉變而導致新的產銷模式及供需生態;三則Intel針對記憶體(DRAM、Flash Memory)已著手計劃WLP的轉型,將大幅採用Wafer-level Packaging的比例。故此股勢力在半導體業界蓄勢待發,尤其以記憶體為大宗的廠商所受的影響較大,但需求時間上在未來三~五年內仍不會明顯,而產品區隔上或許只對特殊的產品或因應特別的產銷狀況而產生。

未來發展及對策

晶圓級封裝(WLP)的提倡,主要仍以晶圓廠的標準製程來取代現有封裝測試的製程,亦即經過晶圓測試、封裝直接以SMT的方式上Board(DIMM/MB),而傳統封裝及測試流程在測試上除Wafer Probe外,封裝完後仍需測試成品的良窳,而將IC SMT至Board後尚須整條DIMM作測試,中間程序繁多所費成本增加許多。且倡議者最主要的論點是簡化IC製造流程,則配合晶圓廠現有設備及材料配合Flip-chip Technology的凸塊製程,以顛覆傳統封裝的生態。未來WLP發展的方向及其影響層面可歸納為以下幾點,相關因應對象則可參考(表三):

1.以記憶體為發展目標,以符合標準化之生產流程。

2.形式打破垂直分工體系,但實質上封裝測試廠仍將扮演一定的分工角色。

3.Design House、晶圓廠及封裝測試廠、記憶體模組廠產銷生態將會產生既競爭又結盟的關係。

4.發展WLP成功與否在於KGD的解決、Solder Bump的供應、市場的需求及生產體系改變的風險承擔性。

5.WLP的發展僅能適用於特定晶片,故不致於大幅影響現有封裝市場的架構,因此,縱使改變產銷生態,但其影響強度不致於太大(特定區隔)。

6.WLP的製程現階段仍將以分工為主,例如:晶圓廠專司晶圓製造、Bumping由專業製造廠提供、封裝廠仍負責Bumping加工後的後段流程,但可發現的是與傳統封裝製程歧異性頗大。

7.因第6點之故,則製造廠、Bumping廠及封裝廠、模組廠可能形成一個新的產銷體系,故短期不致於發生完全由晶圓廠製造的情形發生,此由國內發展情形似可略知一二。

8.若WLP發展順利,則封裝廠一則應以Flip-chip為開發目標,並加強與製造廠、Bumping廠、模組廠的聯盟關係;二則Logics的客戶比例應設法提高,以調合WLP增加所造成的記憶體封裝型態的消長。

TFT-LCD驅動IC帶動TCP封裝

液晶顯示器是利用液態晶體的光學性來達到顯示的效果,即把液態晶體灌入兩片真空的玻璃之間再加上電壓,並適當控制間距,便能改變入射光的偏轉特性。而目前引起國內廠商投資熱潮的TFT即挾其輕薄短小省電的特性,創造出許多電子應用領域,如電子錶、計算機、電子字典、掌上型電視、筆記型電腦,而未來在「後PC時代」使用TFT-LCD將成為許多產品的顯示配備。目前LCD的應用觸角正逐步從筆記型電腦擴展到桌上型電腦監視器,甚至家用電視領域及其他小型的攜帶式產品,產品從大尺寸精細的HDTV及PC監視器,到壁掛電視及投影電視均有跨足,至於筆記型電腦、PDA、電子字典等新興應用領域更是稱霸天下。

相關產品雖然都是應用LCD做為顯示器,但卻是不同的使用目的,因此在產品的設計上,必須具有專業技術來輔助完成,此股趨勢從近來業者大量地投資,及面板供應仍嫌不足的盛況即略知一二。而TFT-LCD驅動IC更是不可或缺的零組件,受到筆記型電腦用TFT-LCD市場需求面的影響,TFT驅動IC的需求也跟著持續增加;同時LCD 監視器的應用急速增加,因此有人預測從1998年下半年至1999年,驅動IC的市場需求將趨緊。

在供應商方面,除了SHARP、東芝、NEC、日立、SEIKO、EPSON廠商之外,TI、Oki、Cirrus、三洋電機也加入生產行列,故主要關鍵技術仍掌握在日韓廠商手中。驅動IC過去多為傳統封裝型態再透過SMT的製程與LCD面板作結合,但隨著LCD要求薄型化之下,已轉由TCP、COG、COF取代之,雖仍有一些對解析度要求不高的LCD仍沿用傳統的SMT結合,但絕大部分已轉成TCP,此方式與Assembly現有製程有不小的差異性存在。

目前驅動IC由於台灣晶圓廠對於製程及IC設計較不成熟,加上初期台灣各TFT-LCD廠多會依據日本合作廠商的驅動IC規格進行採購,沒人願意冒險使用其他貨源,因此生產TFT顯示器所需的驅動IC幾乎都來自日本,而現在能提供驅動IC外銷的日本廠商家數有限,以TI、恩益禧、松下、日立等大廠為主。對於未來大量生產的台灣TFT-LCD廠而言,驅動IC的供貨不足也容易形成發展障礙,而相關產業配套的成熟度亦深深地影響著未來的發展潛力,據悉國內封裝業者日月光、南茂、矽品、華泰及飛信等廠商正積極在開發TCP封裝型態,以因應TFT-LCD驅動IC時代的到來。

由於IC無法直接與玻璃基板結合,因此,必須經由構裝的處理以完成兩者的接合,簡介如下:

1.SMT的接合:

傳統上驅動IC亦經由Assembly做封裝,再經封裝好的IC透過SMT技術銲接在PCB上,再以軟性電路板(FPC)和LCD面板作接合。此方式為最早期的技術,惟隨著面板體積及薄型化的要求下,由於無法達成微間距的條件,因此,漸漸地被其他種封裝型態所取代,但現仍有部分低解析度之面板亦以此做為主要的封裝型態(圖二)。

2.TAB的接合:

TAB的技術就Chip Interconnection的演進而言,主要係為替代Wire Bonding,隨著薄型化之要求,遂成為LCD構裝的主要技術,在日本TAB技術又稱為TCP(Tape Carrier Package),其又可區分兩種型態分別為ILB(Inner Lead Bonding)與OLB(Outer Lead Bonding)。前者,從Tape的設計及製造、Bump的製造內引腳接合及封膠、測試;後者,只捲帶上的引腳與LCD面板及PCB間的接合技術(圖三)。

3.COG(Chip On Glass)的接合:

乃是將直接長好IC的晶片長Bump,再直接接合於LCD的面板上。製程上先將面板清理乾淨(用溶濟或電漿),以ACF(異方性導電膠)接合材料,再將長Bump的IC黏合,此為晶片與玻璃結合的部分,而對於外送的訊號則以FPC(Flexible Print Circuit Board)做媒介。但其缺點為修復不易,若欲維修必可能損害玻璃基板,成本所費不少(圖四)。

4.COF(Chip On Film)的接合:

乃是由TCP技術衍生出來的,將IC及被動元件直接與Film接合,再以ACF做介面材料結合在玻璃基板上。由於此封裝形態重量輕、容易修復、高密度間距構裝,此為目前最新的發展技術(圖五)。

結論

從「後PC時代」衍生而來的資訊家電產品概念,將資訊和家電的優勢結合於一身,是目前大多數廠商較為具體化的概念,以台灣廠商目前對標準所掌握的程度來看,未來要擺脫技術或產品跟隨者的角色並不容易。惟其中還是有一些特殊性的應用產品,台灣廠商仍具有開創的機會,而要在「後PC時代」中佔有先機,產品的差異化以及提升附加價值才能擁有真正的競爭力。

過去台灣封裝業者所面對的客戶大都屬於Fabless,產品多屬標準化,規格、特性均有一定的規範可遵循,但隨著IDM的委外日盛,訂單的規格恐須朝多樣化及機動化方向發展。再者,下游產品種類日益增多,尤其消費性及通訊性產品的興起,著重3C的結合,故晶片的集積度會更加地繁雜,而封裝的需求將會隨著晶片種類的特性及其應用而發生重大變革,不再侷限於現有的產品型態。

相反的,客戶著重的是如何將他們的晶片或構想應用在適合的封裝型態上(Interconnecting the consumer's ideas to the right packages),此意味的是提供客戶合適的封裝型態而非從代工廠商的角度出發,依客戶的產品應用而提供不同的解決方案,此即表示晶片種類即使一樣,但應用途徑不同,可能需使用不同的封裝型態,而未來產品的多樣化將造就差異性的市場,則封裝廠在產品技術的改進及配合客戶的需求上將成為發展重點。

先進的關鍵封裝技術(Wafer Level Package/Flip-chip Package/TCP/3D Package)將隨著下游消費、網路資訊產品的普及而漸趨成熟,而面對「後PC時代」的種種變革將帶動產業間的重新定位,PC將跳脫現有形體限制及傳統所賦予的機能,呈現無所不在的面貌,未來PC將內化成為資訊家電、網路等用品的核心,而且完全異於現有的模式,而多元化的產品將掀起新一波的產業革命,亦將顛覆PC現有的地位。

處於半導體中的封裝業對於此風潮亦不得不尋求新穎及符合市場的突破,而這種變動將是未來封裝業界極需面對的一大課題與挑戰。傳統的封裝型態雖然仍維持其一定的市場需求與定位,但隨著多元化產品的刺激下,將會帶動封裝界的研究發展能力及創新的契機,而先進的封裝產品會成為這一波變動的推進原動力。