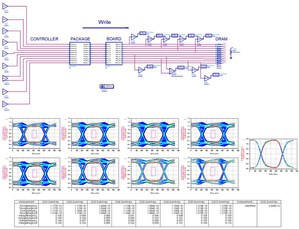

是德科技(Keysight)日前推出DDR匯流排模擬器(DDR Bus Simulator),為可根據JEDEC DDR記憶體匯流排規格產生準確的誤碼率(BER)輪廓的實用工具。該模擬器是Keysight EDA旗下Advanced Design System (ADS) 2014.11軟體新增的選項,可協助工程師快速準確地計算出記憶體介面之DQ和DQS眼圖概率密度分佈和BER輪廓。

|

| /news/2014/10/24/1345276930S.jpg |

此新選項透過統計模擬來執行前述運算,因此不需要冗長的或是耗時的位元碼型。相反的,它利用發射器、通道和接收器脈衝響應,以及概念上為無限的非重複位元碼型之隨機屬性,來建構眼圖。傳統的工具則是透過類SPICE或是迴旋(convolutional)通道模擬等方法來計算有限位元碼型,然後利用其不穩定雙重Dirac外推演算法(dual-Dirac extrapolation)來建構眼圖。

台灣是德科技總經理張志銘表示:「個別執行的模擬既快速又準確,讓設計工程師能在批次處理模式下運作,並且快速探索設計空間。此外,我們還提供DDR匯流排模擬器的分散式運算8套軟體授權,讓工程師能夠將他們的參數掃描結果送入運算叢集中,以便更快獲得答案。」

ADS DDR匯流排模擬器採用嚴謹的DQ和DQS眼圖計算法,方便工程師針對任意的低誤碼率位準,包括JEDEC制定的1E-16輪廓,來建構眼圖。該模擬器可計算上升和下降轉態時間之間的交互干擾和不對稱性,並可提供輪廓和DDR4接收遮罩規格之間完整的時序和電壓邊限。

ADS DDR匯流排模擬器支援內建、IBIS或電路模型等三種不同的IC模型。工程師可在電路圖中任意「混搭」所有這些模型。內建驅動器和接收器分別提供解加強和連續時間線性等化功能。

DS匯流排模擬器和DDR匯流排模擬器分散式運算8套授權將於今年第四季與ADS 2014.11版軟體同步推出。