東芝(Toshiba)公司成功研發出一款適用於類比功率半導體應用的靜電放電(ESD)保護裝置,產品採用先進的0.13μm製程技術製造,最佳化了電晶體結構,顯著提高了靜電放電特性。靜電放電保護穩固性提高多達四倍,標準差僅為傳統結構的十二分之一。3D模擬分析也有助於東芝發現一種機制,最佳化電晶體結構,提高靜電放電穩固性。東芝在2016年6月14日於捷克舉行的國際半導體研討會ISPSD2016上公布了這些創新成果。

|

| 新款靜電放電保護裝置平台嵌入CMOS、DMOS、雙極型電晶體等電晶體及電阻器和電容器等被動元件。 (Graphic: Business Wire) |

注入來自人體或設備的靜電放電電湧,有可能毀壞半導體元件,因為靜電放電電流引起矽材內局部溫度上升。需要靜電放電保護元件來保護內部電路。這對需要施加 10V-100V電壓的類比功率半導體元件來說尤為重要,這些半導體元件需要高額定電壓。在這種情況下,靜電放電保護裝置必須確保大電流,進而導致晶片尺寸增大。縮小靜電放電保護裝置尺寸成為讓晶片更為緊湊的一個問題。

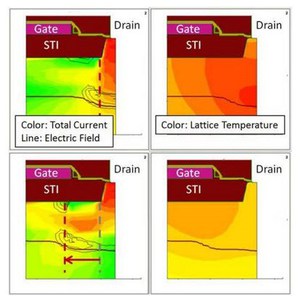

透過靜電放電事件3D模擬分析,東芝發現,流經最高電場點的電流導致晶格溫度上升,進而導致靜電放電誘發的破壞。修改電晶體結構,將漏極低電阻區延伸向源 極方向並抑制橫向矽電阻,將來自漏極底部的電流轉移向源極方向並從最高電場點將其分離。經發現,這一最佳化設計使靜電放電穩固性提高多達四倍,而標準差減少到十二分之一。此外,該裝置確保HBM +/-2000V(註)所需的尺寸減少了68%。

東芝利用0.13μm製程技術,提供先進的類比流程平台,可在該平台嵌入CMOS、DMOS、雙極型電晶體等電晶體以及電阻器和電容器等被動元件。使用者可從以下三個流程平台中選擇適用於每個應用的製程:BiCD-0.13主要用於汽車(DMOS最高可達100V);CD-0.13BL主要用於馬達控制驅 動器(DMOS最高可達60V)以及CD-0.13製程主要用於電源管理IC(DMOS最高可達40V)。

東芝計畫於2017年推出採用CD-0.13製程技術的產品並繼續積極將該製程技術推廣至其他流程平台,以提高靜電放電特性。

註:HBM(人體模型):指示靜電放電穩固性的參數之一