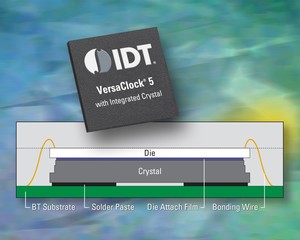

供應關鍵混合訊號半導體方案類比與數位公司IDT推出新版VersaClock 5 可程式化時脈產生器,其內建晶體設計使電子計時系統更簡單更具成本效益。5P49V5933及 5P49V5935提供了IDT VersaClock 5時脈產生器創新的功能,同時藉由晶體整合達到減少電路版的空間及降低成本。透過整合頻率源,設計人員未來在設計時不再需要與外部晶體合併,而將時間花費於因合併繼之而來的頻率調整上。

|

| IDT推出新版VersaClock 5 可程式化時脈產生器,讓設計人員可減少電路板空間,物料清單及設計時間 |

VersaClock 5可程式化計時設備只需要一半的核心功耗即可達到最佳抖動效能,並提供獨立的標準成對輸出,輸出型態包括LVDS, LVPECL,HCSL或雙LVCMOS。此多重輸出計時解決方案具備相當的設計靈活性整合系統組件,使其適合注重成本,且需低功耗、低抖動應用的設計。整合晶體有效地將裝置轉為可程式化石英晶體振盪器,並從設計中將不必要的組件移除。

IDT時序事業群總經理Kris Rausch表示:「我們透過晶體整合至最新版的VersaClock 5裝置,開發了具客戶優勢的獨特創新之時序產品。」「 設計團隊取得原始VersaClock 5的所有優勢-出色的抖動效能及極低功耗-加上不需處理晶體所省下的時間和成本。」

5P49V5933最多可提供兩個輸出頻率,而5P49V5935則可提供多達四個。此裝置提供4×4微米封裝。令人印象深刻的700 fsec RMS相位抖動性能滿足客戶對於1G / 10G乙太網路和PCI Express 1,2,3的需求,以及其他高效能晶片互連,並符合SoC和FPGA對於時脈產生的需求。此裝置特色為具有僅30毫安培的低核心功耗。(編輯部陳復霞整理)