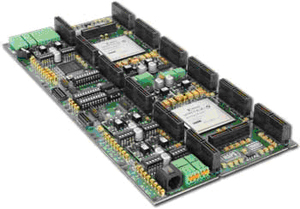

FPGA ASIC原型驗證平台HARDI,日前推出第四代ASIC原型驗證平台HAPS-50系列;該系列的母板是以目前Xilinx Virtex-5 LX330為基準。最先上市的HAPS-52擁有四百萬ASIC閘數的容量,並可與其他HAPS系列相互堆疊或聯結,滿足任何ASIC閘數的需求。預期將讓目前ASIC設計領域,以更高的FPGA容量來更有成效的完成設計與驗證。

|

| FPGA ASIC原型驗證平台 |

HARDI技術長Jonas Nilsson表示,HAPS的系列設計都是基於通用的FPGA驗證平台所設計,因此可以支援業界的泛通用FPGA驗證工具,譬如Synplicity Total Recall、AUSPY的ACE分割工具以及Temento DiaLite的FPGA除錯工具。對於工程師而言,並不會因為選擇HAPS而影響到公司內部現有的CAD流程,反而因為HAPS的通用性而能達到跨部門及重複使用的目的。

HAPS-50系列,也與其他HARDI先前所推出的HAPS-10、HAP-20以及HAP-30所有系列相容;邁吉倫科技總經理指出,FPGA Prototyping就像是高度整合IC的火車頭,帶領著IC產業前進,當火車頭尚未完備,整個產業勢必也將因此也停滯,而HAPS-50系列的誕生,無疑是對國內ASIC原型驗證平台注入一股強大的動力,加速產業的邁進。