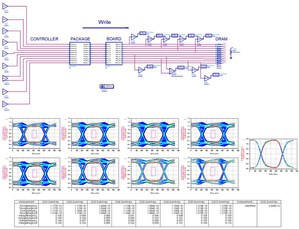

是德科技(Keysight)日前推出DDR总线仿真器(DDR Bus Simulator),为可根据JEDEC DDR内存总线规格产生准确的误码率(BER)轮廓的实用工具。该仿真器是Keysight EDA旗下Advanced Design System (ADS) 2014.11软件新增的选项,可协助工程师快速准确地计算出内存接口之DQ和DQS眼图概率密度分布和BER轮廓。

|

| /news/2014/10/24/1345276930S.jpg |

此新选项透过统计仿真来执行前述运算,因此不需要冗长的或是耗时的位码型。相反的,它利用发射器、信道和接收器脉冲响应,以及概念上为无限的非重复位码型之随机属性,来建构眼图。传统的工具则是透过类SPICE或是回旋(convolutional)信道仿真等方法来计算有限位码型,然后利用其不稳定双重Dirac外推算法(dual-Dirac extrapolation)来建构眼图。

台湾是德科技总经理张志铭表示:「个别执行的仿真既快速又准确,让设计工程师能在批处理模式下运作,并且快速探索设计空间。此外,我们还提供DDR总线仿真器的分布式计算8套软件授权,让工程师能够将他们的参数扫描结果送入运算丛集中,以便更快获得答案。」

ADS DDR总线仿真器采用严谨的DQ和DQS眼图计算法,方便工程师针对任意的低误码率位准,包括JEDEC制定的1E-16轮廓,来建构眼图。该仿真器可计算上升和下降转态时间之间的交互干扰和不对称性,并可提供轮廓和DDR4接收屏蔽规格之间完整的时序和电压边限。

ADS DDR总线仿真器支持内建、IBIS或电路模型等三种不同的IC模型。工程师可在电路图中任意「混搭」所有这些模型。内建驱动器和接收器分别提供解加强和连续时间线性等化功能。

DS总线仿真器和DDR总线仿真器分布式计算8套授权将于今年第四季与ADS 2014.11版软件同步推出。