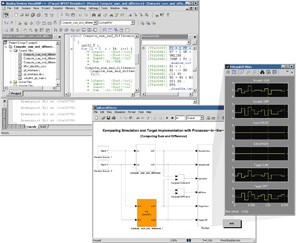

The MathWorksR和美商亞德諾(Analog Devices),共同發表最新驗證工具:ANALOG DEVICES VISUALDSP++ 連結工具(Link for ANALOG DEVICES VISUALDSP++),將整合MATLAB、Simulink和美商亞德諾公司(Analog Devices, Inc.)所開發的Analog Devices VisualDSP++產品,提供程式設計者一個可供開發及除錯的軟體環境。

|

| /news/2007/06/28/1710468057.jpg |

The MathWorks在台總代理鈦思科技表示,工程人員可利用ANALOG DEVICES VISUALDSP++ 連結工具(Link for ANALOG DEVICES VISUALDSP++),驗證在VisualDSP++軟體上所執行的嵌入式程式碼,亦可驗證從Simulink模型所產生的VisualDSP++物件。這個新的模組能夠加速訊號處理和控制演算法在Analog Devices處理器上的開發及驗證速度;藉此,能夠大幅減低手寫產生程式碼的錯誤機率。

鈦思科技表示,利用ANALOG DEVICES VISUALDSP++ 連結工具(Link for ANALOG DEVICES VISUALDSP++)的模型化設計(Model-Based Design)概念,可協助航太/國防、汽車、通訊及電子等產業的工程人員進行Analog Devices處理器的設計和開發。此一模組具可支援美商亞德諾公司(Analog Devices, Inc.)開發的Analog Devices BlackfinR、SHARCR和TigerSHARCR等處理器。現在,相同的模型可運用在嵌入式軟體開發環境的模型化基礎設計的四個階段—可執行的規格、設計模擬、產生嵌入式程式碼及驗證。

ANALOG DEVICES VISUALDSP++連結工具(Link for ANALOG DEVICES VISUALDSP++)能夠和VisualDSP++整合開發及除錯環境(integrated development and debugging environment,IDDE)緊密地結合。這套模組能夠讓工程人員直接從MATLAB執行VisualDSP++指令,並進一步進行分析、除錯、及程式碼的驗證等工作。它同時能夠針對有支援的控制器所自動產生的subsystem code,進行控制器迴路(processor-in-the-loop, PIL)的協同模擬。經由演算法及系統設計過程中不斷驗證的。Simulink模型,可減少在嵌入式處理器上測試嵌入式程式碼的時間。這項系統層測試平台(test-bench)的功能可讓系統工程師快速地在嵌入式處理器上驗證他們的設計是否正確,而不用花時間以人工方式寫出演算法,或者另外撰寫不同的test-bench,這相對減少需要利用不同工具進行驗證的需求。