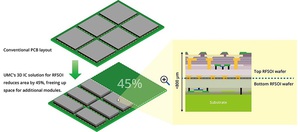

聯華電子今(2)日推出業界首項RFSOI製程技術的3D IC解決方案,此55奈米RFSOI製程平台上使用的矽堆疊技術,在不損耗射頻(RF)效能下,可將晶片尺寸縮小45%以上,客戶能夠有效率地整合更多射頻元件,以滿足5G更大的頻寬需求。

|

| 聯電的RFSOI 3D IC解決方案可減少電路板晶片所占面積達45%,支援 5G 行動裝置中整合更多射頻元件。 |

RFSOI是用於低雜訊放大器、開關和天線調諧器等射頻晶片的晶圓製程。隨著新一代智慧手機對頻段數量需求的不斷增長,聯電的RFSOI 3D IC解決方案,利用晶圓對晶圓的鍵合技術,並解決了晶片堆疊時常見的射頻干擾問題,將裝置中傳輸和接收資料的關鍵組件,透過垂直堆疊晶片來減少面積,以解決在裝置中為整合更多射頻前端模組帶來的挑戰。該製程已獲得多項國際專利,準備投入量產。

RFSOI解決方案系列從130到40奈米的製程技術,以8吋和12吋晶圓生產,目前已完成超500個產品設計定案,出貨量高達380多億顆。此外,聯電的6吋晶圓廠聯穎光電提供化合物半導體砷化鎵(GaAs)和氮化鎵(GaN),以及射頻濾波器(RF filters)技術,可充分滿足市場對射頻前端模組應用的各種需求。