ASIC设计服务暨IP研发销售厂商─智原科技推出智原最新开发的miniPLL组件。相位锁定回路(Phase-Locked Loop)在现今SOC电路设计的领域中相当重要,广泛被运用在频率同步(Clock Synchronization)与相位追踪(Phase Tracking)电路,像是频率合成器(Frequency Synthesizer)、频率产生器(Clock Generator)与频率及数据回复电路(Clock/Data Recovery Circuit, CDR)。

|

| /news/2004/12/22/1718258789.jpg |

然而在晶体管持续微缩(scale down)的竞赛中,模拟电路诸如PLL却无法获得像一般数字电路所能得到的面积缩小、高效能、低功耗等种种优点。而同时在scale down的情况下,所供应的电压也必定下降,无可避免导致信号的摆幅要有所缩减,可是许多电路组件噪声(Noise)并不会因此下降,如电阻的每单位带宽热噪声(thermal noise)电压值,与信号的大小或频率是没有关系的,同时,晶体管上一些跟体积、面积有关的参数值也会跟着下降,导致原本可以忽略的非线性杂散效应也必须要加以考虑。有鉴于此,智原在投入可观的研发人力和资源后获得此项技术的重大突破。

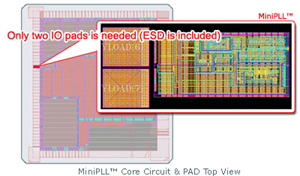

miniPLL是目前能在不牺牲jitter及performance情况下,所做到全球最小且可程序化的PLL,不但大幅地节省了功耗,且仅仅只需要两个IO slots就能够完成,在完全没有浪费芯片内部core的面积之下,大大的减少了芯片的尺寸,同时非常有效地提高设计人员在设计上的弹性。