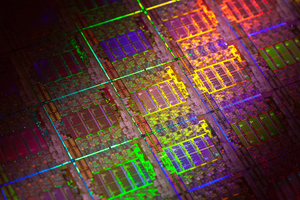

Mentor Graphics公司(明導)宣佈與三星電子合作,為三星代工廠10奈米FinFET製程提供各種設計、驗證、測試工具及流程的優化。其中包括Calibre物理驗證套件、Mentor Analog FastSPICE(AFS)平台、Olympus-SoC數位設計平台和Tessent測試產品套件。這些工具皆經過優化和認證,使系統晶片(SoC)設計工程師能夠快速適應三星代工廠先進的10奈米製程,並且對第一次試產就能成功有極大的信心。

|

| Mentor Graphics優化工具和流程,協助設計工程師成功應對三星代工廠10奈米FinFET製程 |

設計風格和製造製程之間的相互作用在10奈米會變得更為重要,因此可製造性設計(DFM)工具在驗證流程中發揮關鍵作用。三星代工廠已對Calibre YieldEnhancer產品,特別是其SmartFill和 ECO/Timing-Aware Fill功能進行認證,幫助設計工程師在多次更改設計的情況下,仍能滿足製造製程平坦化要求,趕上交付製造期限。為了幫助設計工程師發現和解決潛在的微影相關問題,三星支援 Calibre LFD工具的使用,該工具是基於Mentor的製程process-window modeling、光罩合成、光學鄰近效應修正(OPC)和解析度增強(RET) 的量產製造方案。

由於設計團隊可同時處理多個 DFM 元素,他們可使用建在Calibre Yield Analyzer工具上的三星 DFM評分和分析解決方案以簡化決策權衡流程。最後為把製造結果快速回饋到客戶設計流程中,三星使用 Calibre Pattern Matching 作為識別造成低良率的圖形並予以修正的解決方案。

在物理驗證方面,Calibre nmDRC平台經認證可用於10奈米製程,並成為三星研發、IP驗證和無晶圓廠客戶設計交付製造的生態系統中標準驗收簽核方案。三星使用Calibre Multi-Patterning 作為三重曝光和四重曝光的製造製程開發在多年的合作後得到成功。

三星代工廠已認證 Calibre xACT能夠於10奈米中提供高精度和高性能的寄生參數提取。Calibre xACT工具使用整合的場求解器(field solver)來計算複雜三維 FinFET結構的寄生參數。它經由高度可擴展的平行處理方法進行性能優化。

其他認證則有助於SoC設計工程師進行電路驗證、物理應用和IC測試。例如,AFS平台得到三星10奈米製程元件模型和設計套件的認證。共同的客戶使用AFS,為類比、射頻、混合信號、記憶體和客製化數位電路的驗證,提供比傳統SPICE模擬器速度更快的奈米級的SPICE精確度。

Olympus-SoC佈局和佈線平台也已經過認證,可用於10奈米製程,具有全面的著色設計方法,包括底層規劃、佈局、寄生參數抽取、佈線和晶片完成要求。為了解決FinFET製造製程中的特殊挑戰,該平台支持M1三重曝光、色移(color shifting)、非一致佈線通道、光罩和寬度依賴間距規則以及其他新增功能。有多個共同客戶正在使用該工具進行設計。

在測試方面,Mentor和三星已展開合作,使Tessent測試產品套件可為新單元結構提供10奈米級更佳的測試品質,同時為更大規模的10奈米設計測試提供更高的測試圖形壓縮率進而控制成本。兩家公司還利用生產測試診斷來快速識別和消除設計試產擴量階段出現的特定於設計和影響良率的單元特徵。

「我們與三星代工廠的合作遠非僅僅是將這一先進的製程帶給我們共同的客戶,」Mentor Graphics Design to Silicon部門副總裁兼總經理Joe Sawicki說道,「此整合解決方案貫穿於設計驗證、製造和測試中,為無晶圓公司和三星代工廠之間建立起了高度整合的橋樑。」