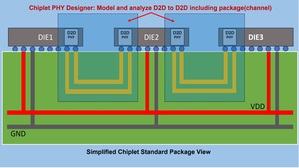

是德科技(Keysight)推出Chiplet PHY Designer,這是該公司高速數位設計與模擬工具系列的最新成員,提供晶粒間(D2D)互連模擬功能,可對業界稱為小晶片(Chiplet)之異質和3D積體電路設計的效能進行全面驗證。新的電子設計自動化(EDA)工具提供深度建模和模擬功能,讓小晶片設計人員能夠快速準確地驗證其設計是否符合通用小晶片互連(UCIe)標準的規格。

|

| 是德科技推出Chiplet PHY Designer |

UCIe已成為半導體產業最重要的小晶片互連規格。這個開放標準定義了先進2.5D或3D封裝中小晶片的互連方式。許多頂尖的半導體設備和EDA工具供應商,以及晶圓廠和小晶片設計工程師,都已開始支援或採用UCIe標準。當更多設計人員使用此互連標準,來確保其小晶片的效能符合規格,業界便可建立一個致力於實現小晶片互通性和商業化的廣泛生態系統。