三星電子今日宣布,已開發出業界首個12層的3D-TSV(Through Silicon Via)技術。此技術透過精確的定位,把12個DRAM晶片以超過6萬個以上的TSV孔,進行3D的垂直互連,且厚度只有頭髮的二十分之一。

|

| /news/2019/10/07/2042046200S.jpg |

三星指出,該技術封裝的厚度(720um)與目前的第二代8層高頻寬記憶體(HBM2)產品相同,能協助客戶推出具有更高性能與容量的次世代儲存產品,且無需更改其系統配置。

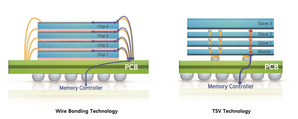

此外,新3D封裝技術還具有比現有的引線鍵合技術短的晶片間數據傳輸時間,能顯著提高速度並降低功耗。

三星電子TSP(測試與系統封裝)執行副總裁Hong-Joo Baek表示,隨著各種新的高性能應用的出現(如AI和HPC),能整合所有複雜的超高性能記憶體的封裝技術變得越來越重要。隨著摩爾定律達到其極限,預計3D-TSV技術的作用將變得更加關鍵。

此外,透過將堆疊層數從8個增加到12個,三星表示將很快能夠量產24 GB高頻寬記憶體,其容量是當今市場上8GB的三倍。