西門子數位化工業軟體與矽品精密工業(矽品;SPIL)合作,針對 SPIL 扇出系列的先進(IC)封裝技術,開發和實作新的工作流程,以進行 IC 封裝組裝規劃與 3D LVS(layout vs. Schematic)組裝驗證。此流程將被運用於 SPIL 的 2.5D 和扇出封裝系列。

|

| 西門子與SPIL攜手為扇出型晶圓級封裝提供3D驗證工作流程 |

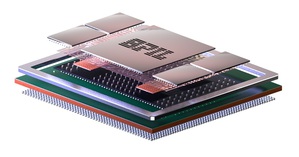

為了滿足全球市場對於高效能、低功耗、小尺寸 IC 的上漲需求,IC 設計中的封裝技術也變得日益複雜,2.5D 和 3D 配置等技術因應這種挑戰而出現。這些技術將一個或多個不同功能的 IC 與較高的 I/O 和電路密度相結合,因此必須能建立和檢視多個組裝和 LVS、連線關係、幾何形狀與元件間距情境。為了幫助客戶輕鬆部署這些封裝技術,SPIL 選用西門子的 Xpedition Substrate Integrator 軟體與 Calibre 3DSTACK 軟體,用於其先進扇出系列封裝技術的封裝規劃及 3D LVS 封裝組裝驗證。

矽品精密工業股份有限公司研發中心副總王愉博博士表示:「矽品所面對的挑戰是要開發和部署一個經過驗證且包括全面的 3D LVS 的工作流程,來進行先進封裝組裝規劃和驗證。西門子是該領域公認的領導廠商,擁有穩健的技術能力並獲得市場的認可。矽品將在今後的生產中使用與西門子共同打造的流程來驗證我們的扇出系列技術。」

SPIL 的扇出封裝系列能夠提供更大的空間,方便在半導體區域頂部進行更多 I/O 佈線,並經由扇出製程擴大封裝的尺寸,而傳統的封裝技術無法做到這一點。

西門子數位化工業軟體電路板系統高級副總裁 AJ Incorvaia 表示:「西門子很高興與 SPIL 攜手合作,為其先進封裝技術定義和提供必要的工作流程和技術。隨著 SPIL 的客戶繼續開發複雜性更高的設計,SPIL 與西門子也隨時準備好為其提供所需的先進工作流程,將這些複雜設計快速推向市場。」