本周IEEE国际电子会议(IEDM)上,比利时微电子研究中心(imec)发表了最新的半镶嵌整合方案,透过导入VHV绕线技术(vertical-horizontal-vertical)来实现4轨(4T)标准单元设计,加速元件微缩。该半镶嵌制程成功将标准单元在中段制程的端到端间距(tip-to-tip;T2T)微缩至8奈米,不同元件层的边缘还能完成自对准。设计人员可透过这项微缩技术来实现更紧密的标准单元堆叠,与5轨设计相较,面积减少了21%。这套创新的布线方案搭配半镶嵌整合制程,将能逐步推进逻辑元件的微缩蓝图,迎向埃米世代。

|

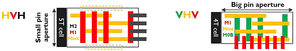

| 图一:标准单元样板的俯视图(左)5轨HVH绕线设计(右)4轨VHV绕线设计。 |

长久以来,中段制程采用单层接点的设计来连接前段制程(FEOL)与後段制程(BEOL)。但到如今,中段制程的元件层逐渐增加,例如包含Mint金属层与Vint通孔层。这些元件层将源极、汲极与闸极的电讯号传输至局部导线层,或是反向传输。

imec近期推出了一套创新的标准单元布线架构,取名为VHV,透过在中段制程增设一层元件层(M0B)来实现4轨设计,加速元件微缩。利用这项技术,标准单元的前三层布线采用VHV设计,而非5轨标准单元所用的传统HVH绕线设计。不过这项创新的双层VHV绕线技术在制程整合方面极具挑战,主要原因是4轨标准单元之间的边缘较为狭窄。在中段制程,相邻的M0B层导线端点必须紧密相距,相向的两条通孔(VintB)边缘也需清晰的轮廓分界,所有间距都至少在顶部Mint金属层的关键尺寸(CD)之内。展??未来技术节点,我们必须将导线的端到端间距与通孔层的间距从24奈米逐渐缩短至8奈米。直接蚀刻已经无法实现这项目标,因此需要改用自对准图形化策略。

在今年的IEEE国际电子会议(IEDM)上,imec展示一项双层半镶嵌技术,用来实现紧密相邻的标准单元图形定义,其中进行一次直接金属蚀刻。imec奈米导线研究计画主持人Zsolt T?kei表示:「大致来说,我们先用传统图形化技术,制出连续导线与较宽的通孔,接着制出两层金属层,随即把这些元件层一分为二,将位於顶部、间距为16nm~18nm的Mint金属层作为硬光罩,完成最後的图形化处理。」 如此一来就能实现Mint、VintB与M0B三层元件层的同步自对准。透过以??金属制成的双层测试元件,我们取得了重大的研究成果,通孔的平均关键尺寸仅有10.5nm,M0B层的端到端间距也只有8.9nm。」 导线电阻与隔离特性等初始电性特徵分析也协助进行了结构验证。

Zsolt T?kei接着说道:「这项VHV绕线技术将是实现A10、A7、A5、A3等埃米技术节点的关键微缩技术,有效缩短标准单元的间距。甚至还能用於新兴的元件架构,像是奈米片、叉型片与互补式场效电晶体(CFET)。透过在中段制程导入以往用於後段制程的半镶嵌技术,我们现在也找到了整合这项绕线技术的方法。但这还需要更详细的研究。为此,imec正在进行全新光罩设计的下线制造。」