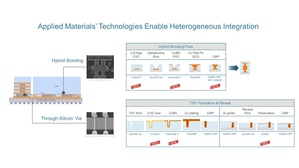

面对当前国际半导体市场竞争加剧,应用材料公司也趁势推出新式材料、技术和系统,将协助晶片制造商运用混合键合(hybrid bonding)及矽穿孔(TSV)技术,将小晶片整合至先进2.5D和3D封装中,既提高其效能和可靠性,也扩大了应材在异质整合(heterogeneous integration, HI)领域领先业界的技术范畴。

|

| 应用材料公司最新推出精进异质晶片整合方案,帮助晶片制造商运用混合键合及矽穿孔技术 |

应材表示,该公司目前身为异质整合(HI)技术最大供应商,提供经过优化的晶片制造系统,包括蚀刻(ETCH)、物理气相沉积(PVD)、化学气相沉积(CVD)、电镀(ECD)、化学机械研磨(CMP)、退火与表面处理。

如今透过混合键合及矽穿孔等全新攻略的核心要件技术,可通过直接铜对铜键合来连接晶片对晶圆和晶圆对晶圆,在更小的空间内堆叠更多导线,缩短讯号传输的距离,进而提高生产率(throughput)和功率。使其组合後的整体成为单一产品的形式来运作,协助半导体业者将各种功能、技术节点和尺寸的小晶片结合到先进封装中,解决产业正受到高效能运算(HPC)和人工智慧(AI)等应用对电晶体的需求以指数级速度成长,而传统的2D微缩速度趋缓且变得更加昂贵等挑战。

应用材料公司半导体产品事业群??总裁暨HI、ICAPS(物联网、通讯、汽车、电源和感测器)和磊晶技术部门总经理桑德·瑞马摩西(Sundar Ramamurthy)博士表示:「如今异质整合技术正快速发展,起因於传统2D微缩已不能同时改进效能、功率和成本,而异质整合则能协助晶片和系统公司突破此一限制,可以在2.5D和3D结构中配置封装更多的电晶体和导线,让晶片制造商得以全新方式改善晶片的功率、效能,降低功耗、单位面积成本与上市时间(PPACt)。」

因此提供的「Insepra SiCN」沉积系统,扩展了应材领先业界的混合键合产品组合,使用一种新的矽碳氮 (SiCN)材料,提供产业中最高的介电键合强度,并具有优异的铜扩散阻障性。更强的介电键合提供了设计人员所需的结构稳定性,能够在给定区域内整合更多铜对铜互连,从而降低功耗并提高元件效能。

「Catalyst CMP」解决方案帮助客户控制「表面凹陷」(dishing)量,亦即在後续高温退火作业步骤中将键合的两个表面上的铜材料预留凹陷。过多的CMP凹陷在铜垫片的顶部表面造成不必要的金属损失,进而产生空气间隙并降低铜对铜键合的真确度(fidelity)和强度。应材的Catalyst解决方案属於动态温度控制技术,可以控制表面凹陷、提高生产率。

至於已在大规模量产中使用超过十年的矽穿孔(TSV)技术,则是用於精确连接堆叠晶片的垂直导线,透过在矽晶片中蚀刻沟槽,然後填充绝缘衬垫和金属导线来完成 TSV。随着设计人员继续将更多的逻辑、记忆体和特殊功能晶片整合到先进的2.5D和3D封装中,每个封装中的TSV互连导线数量已从几百个扩展到数千个。

为整合更多的互连导线并容纳更高的晶片堆叠,设计人员需将矽穿孔变得更窄、更高,造成沉积均匀性改变,因而降低了效能,也增加了电阻和功耗。应材推出的介电质和金属沉积新技术,提供更高的矽穿孔深宽比,协助晶片制造商实现整合、效能和功率的目标;新的沉积系统也能提升运用矽穿孔技术所堆叠晶片的密度、效能、品质和成本

其中包括:「ProducerR InVia 2 CVD」系统是新的化学气相沉积(CVD)制程,在不断增加的各种TSV应用,为需要极端深宽比的逻辑和记忆体客户,提供介电衬垫均匀性和电气特性稳定性(robust)。该系统使用专有的原处(in-situ)沉积制程,为高深宽比的TSV提供了优异的一致性;其生产率也高於原子层沉积(ALD)技术,因此降低了TSV的每片晶圆的成本,并且进一步促进扩展其导入。

「Endura Ventura 2 PVD」物理气相沉积系统提供高达20:1的深宽比,使其广获采用的前代方案能延伸到TSV应用中,提高对金属TSV导线沉积的控制并确保能完全填充,以实现高电气性能和可靠性。新的TSV PVD制程已经与Producer InVia 2 CVD制程完成协同最隹化,为客户提供了解决最具挑战性TSV设计的成熟解决方案,并获得所有先进的晶圆代工/逻辑晶片制造商和所有主要DRAM生产商所采用。

应材最新一代的「Producer Avila PECVD」电浆辅助化学气相沉积系统,是针对TSV的导孔「露出」(reveal)制程应用而设计的。在TSV的制程中,晶圆与暂时的玻璃或晶矽载体暂时性键合,然後透过CMP和蚀刻进行薄化,直至触及TSV。完成TSV露出步骤之後,运用等离子增强的(plasma-enhanced)CVD技术沉积一个薄的介电层,藉此将TSV之间以电气相互隔离。如果PECVD制程产生的热量超过约200。C,脆弱的暂时性键合黏着层可能会受损,导致成本高昂的晶圆良率损失。应材的Producer Avila PECVD系统,能以超低温、高速产生高品质的介电薄膜,满足TSV品质和成本所要求的低热量积存(thermal budgets)和高生产力要求。