ARM与益华计算机(Cadence Design Systems, Inc.)今天宣布,第一个高效能ARM Cortex-A7处理器的14奈米测试芯片设计实现投入试产,预计将生产出高效低功耗的ARM处理器,且藉由Cadence RTL-to-signoff流程精心设计,这个芯片率先以Samsung14奈米FinFET制程为目标,加速迈向高密度、高效能和超低功耗SoC的永无止境的进程,满足未来智能型手机、平板计算机和其他所有先进行动装置的需求。

|

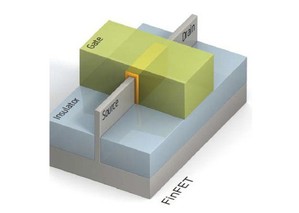

| 14奈米Fin FET结构示意图。 BigPic:620x441 |

除ARM Cortex-A7处理器之外,这个芯片还包含ARM ArtisanR标准单元库(standard-cell libraries)、新一代内存和一般用途IO。这个测试芯片是运用Cadence RTL-to-signoff流程设计,包括Encounter RTL Compiler、Encounter Test、Encounter Digital Implementation System、Cadence QRC Extraction、Encounter Timing System与Encounter Power System。这项成就是在FinFET技术之上实现以ARM技术为基础的SoC之既定计划中不可或缺的一环。

ARM实体IP事业部副总裁兼总经理Dipesh Patel博士表示:「透过顶尖技术与卓越研发的组合,而且很早就和Samsung与Cadence展开合作,在Samsung先进低功耗制程上的ARM最高能效率应用处理器终于投入试产。」

「Cadence益华计算机的先进节点设计流程,搭配我们与ARM和Samsung的组合,对半导体公司迈进14奈米FinFET制程设计来说致关重要。」Cadence益华计算机芯片实现事业群研发资深副总裁徐季平博士在共同声明中表示。

三星电子装置解决方案事业部系统LSI基础架构设计中心资深副总裁Kyu-Myung Choi博士表示:「我们与ARM和Cadence合作,让我们能够随着Samsung开发这项行动多媒体应用的新制程技术而快速创新。」

14奈米制程投入量产,不仅在全球半导体业界是项创举,且意味功能更先进更低耗能的半导体将出现市场上,将进一步提升消费性电子产品的性能。