隨著市場對於更小巧、更節能和更高效能的IC需求日益提升,IC設計界也面臨著嚴苛挑戰。西門子數位化工業軟體更在近日推出Tessent Multi-die軟體解決方案,協助客戶加快和簡化基於2.5D和3D架構的新一代複雜多晶粒設計的積體電路(IC)關鍵可測試性設計(DFT),促進 3D IC 成為主流應用。

|

| 西門子推出 Tessent Multi-die 解決方案,促進 3D IC 成為主流應用。 |

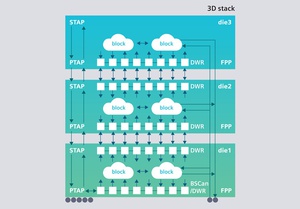

基於下一代電子元件正傾向於採用複雜的2.5D和3D架構,以垂直(3D IC)或並排(2.5D)方式連接多個晶粒,使之能夠作為單一元件運作,卻因為目前大部分的傳統測試方法都是基於常規2D流程而來,為晶片測試領域帶來巨大挑戰。

西門子則為了克服這些挑戰而推出Tessent Multi-die全面DFT自動化解決方案,應用於2.5D及3D IC設計相關複雜度更高的DFT任務,能與西門子 Tessent TestKompress Streaming Scan Network軟體和 Tessent IJTAG 軟體搭配使用,實現每個區塊的DFT測試資源最佳化,而毋須擔心影響其他設計,從而簡化了 2.5D 及 3D IC的 DFT 任務。現在客戶的IC設計團隊,只要使用 Tessent Multi-die軟體,就能快速開發出符合IEEE 1838 規範的2.5D和3D架構硬體。

西門子數位化工業軟體副總裁兼Tessent業務單位總經理Ankur Gupta指出:「目前在2.5D 和3D元件中,採用高密度封裝晶粒的設計需求正快速增長,IC 設計公司也面臨著急劇加增的 IC 測試複雜難度。透過西門子最新的 Tessent Multi-die 解決方案,能夠為客戶未來的設計做好充分準備,同時大幅減少DFT工作量,降低當前製造測試成本。」

除了支援 2.5D 及 3D IC 設計的全面測試之外,Tessent Multi-die 解決方案還可以產生 die-to-die 間的連線測試向量,並使用邊界掃描描述語言(BSDL)執行封裝層級測試。進而利用西門子Tessent TestKompress Streaming Scan Network軟體的封包資料遞送能力,支援彈性平行埠(FPP)技術的整合。

於 2020 年推出的Tessent TestKompress Streaming Scan Network,就將核心級DFT需求從晶片級的測試交付資源中分離出來,使用真實、有效,且自下而上的流程來實現DFT,從而顯著簡化DFT規劃和實作,同時將測試時間縮短4倍。

Pedestal Research 研究總監兼總裁 Laurie Balch 指出:「隨著時間推移,傳統的 2D IC 設計方法將遇到各種限制,越來越多的設計團隊開始利用2.5D及3D IC 架構,以滿足其在功耗、效能及晶片尺寸等方面的要求。在新設計案中部署這些高級方案的首要步驟就是制定 DFT 策略,以應對複雜架構帶來的種種挑戰,從而避免成本的增加或者拖累產品上市時間。透過持續發展 DFT 技術,滿足多維度設計需求,EDA 廠商將進一步推動2.5D 及 3D 架構在全球範圍?的應用。」