儘管EDA(電子設計自動化)大廠近年來持續致力於先進製程的開發工具的開發再輔以不斷強化IP陣容的作法,這有助於縮短SoC(系統單晶片)的開發時程,但事實上,綜觀終端系統設計,混合訊號與類比電路仍然是不可或缺的一環,身為EDA大廠之一的Cadence(益華電腦)仍然相當關注該領域的工具研發。

|

| /news/2014/08/08/1634210250S.JPG |

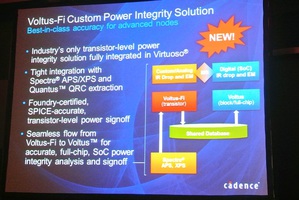

Cadence數位簽核部門產品行銷總監Jerry Zhao指出,綜觀晶片開發流程在進行驗證(Verification)後,還有一道重要的程序,稱為「簽核」(Sign off)。它的功能類似於晶片設計流程的最後一道關卡,用於最後晶片設計的流程之用。在去年11月,Cadence就推出了以SoC為主的簽核工具:Voltus,而在今年八月,Cadence正式發表Voltus-Fi,用作電晶體層級的電性測試,偏重類比、混合訊號與電源管理等晶片。

Jerry Zhao比喻,將晶片視為一座城市的電網,電壓在傳輸的過程勢必會有電壓不足的情形,這就必須透過升壓方式繼續傳送電壓,以讓整個電網都能充分使用到電力。同理,晶片本身也會有類似的情形,一旦電壓不足就無法驅動晶片運作,如此一來也會造成晶片本身的可靠度下降,透過Voltus-Fi的精準量測就有辦法測出晶片內部各個部份的電性狀況,避免在進入Type out的程序造成不必要的成本損失。

由於Voltus-Fi標榜精準量測的特性,Jerry Zhao不諱言,只要是內有電晶體的晶片皆能一體適用,像是內建ADC(類比數位訊號轉換器)的MCU(微控制器)‧應用處理器、電源管理晶片、IGBT甚至是獨立的ADC等,Voltus-Fi都有辦法加測量,所以市場客戶相當廣泛。Jerry Zhao透露,ADI曾經就在3月的公開場合中,展示如何使用Voltus-Fi來進行產品開發,獲得不少好評。

然而,Jerry Zhao也不諱言,這種產品概念,Cadence早在十幾年前便已經提出,只不過先前Cadence歷經了低潮期,這方面的投資研發力道便少了許多,不過在這兩年左右的時間,Cadence又開始急起直追,相信要在簽核領域中居於領導地位,只是時間上的問題。