英特爾(Intel)於週二(2/13)發表一個內含80顆核心的兆級運算(Tera Scale)可編程處理器(programmable processor)。該晶片面積僅指甲般大小(275平方公厘),卻擁有同於超級電腦等級的運算能力,能提供每秒數兆次浮點運算(Teraflops)的效能,同時耗電量更低於目前的家電產品。該晶片目前仍處於實驗室開發階段,未來將有可能應用至電腦、手機等其他電子裝置上。

|

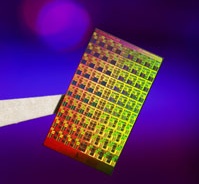

| 英特爾(Intel)發表80核心具備兆次級運算的處理器,每個核心內皆含有兩個浮點運算的引擎(圖片提供:Intel) |

此晶片是英特爾兆級運算研究專案其中一個研發成果。該專案成立至今僅約1年多,目前已有100多個研究項目正在進行中,主要範疇是在微處理器(Microprocessor)、平台(Platform)、程式設計(Programming)等三個領域上,目前著重的研究方向為處理器的多核心架構、彈性設計、電能節省,以及平台模組的3D記憶體架構研發。

英特爾中國研究中心總經理杜江凌博士表示,此晶片的研發成功乃是處理器設計上的一大突破。它是以瓷磚(Tiled)的方式拼貼而成,共結合了80顆相同的處理器,而每個核(Core)上都具備運算及通訊單元,能單獨進行運算並與週遭的處理器進行溝通,串成一個網狀的運算網路。

這樣的設計方式將可大幅縮減處理器的設計時程,更可以達到模組化(Modular)及客製化(Scalable)的目的。杜江凌博士表示,未來工程師只要”copy and pasted”就能完成處理器的設計。但杜江凌博士也指出,多核心架構的設計並不在於核數的多寡,而在於應用的效能上,這就取決於設計者的能力,看其是否具備良好的應用彈性。

除了設計簡捷之外,新的處理器也具備優越的節電效能,由於每個核心內都具有控制單元,能自由控制運作與否,因此只要將在待命及暫時無作用的核關閉,便可大幅縮減電力的消耗,在節能上具有極高的效能。以目前的設計來說,要達到1.01兆級浮點運算的性能,大約只需消耗62W的電力。

杜江凌博士並指出,此多核心架構未來還會更進一步發展,將在其上堆疊記憶體(3D Stacked Memory),也就是利用核心上預留的Z軸通訊線路,來連接記憶體,屆時將可更大幅的提高處理器的效能,而這個技術約有可能在1年內實現。

目前此晶片仍未有具體的產品及上市計畫,但杜江凌博士表示,將有可能應用在複雜而小型的產品,如手機上。杜江凌博士也強調,產品並不是此晶片的研發重點,重要的是技術的提出,並且促使更多的應用需求被實現。