在本週舉行的 2024年IEEE國際電子會議(IEDM) 上,比利時微電子研究中心(imec)展示了一項突破性的技術創新:基於互補式場效電晶體(CFET)的雙列標準單元架構。這種設計採用了兩列CFET元件,並共用一層訊號佈線牆,成功實現製程簡化與顯著的面積縮減,為邏輯元件和靜態隨機存取記憶體(SRAM)開闢了微縮新途徑。

|

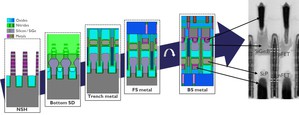

| 這張特寫為一顆單片式CFET技術展品的穿透電子顯微鏡(TEM)影像,該元件製於imec的12吋晶圓研發無塵室(A. Vandooren等人,2024年IEEE國際電子會議) |

根據imec的設計技術協同優化(DTCO)研究,相較於傳統單列CFET,雙列CFET架構將標準單元高度從4軌縮減至3.5軌。在SRAM單元的應用中,這種設計可實現 15% 的面積縮減,若與14埃米(A14)奈米片技術相比,雙列CFET架構的SRAM面積甚至縮減超過 40%。埃米是1奈米10分之1的長度單位。

該技術的核心在於雙列CFET元件共用一條中間佈線牆(middle routing wall),省去了製造極高深寬比通道的需求,進一步簡化了中段製程流程並降低成本。此外,imec的虛擬晶圓廠概念和實驗室技術驗證,證明此新架構能與現有製程技術順利接軌。

imec在會議上展示了一顆功能性單片CFET元件,其晶背具備直接連接到底部pMOS元件源極/汲極的接點。這項創新採用了極紫外光(EUV)圖形化技術,確保晶背的功率與訊號佈線密度,並實現了晶圓正面與晶背接點的高精度對齊(精度小於3奈米)。

imec的DTCO研究計畫主持人Geert Hellings表示:「從7埃米邏輯節點開始,CFET元件的應用將取代環繞閘極(GAA)奈米片架構,並為功率、性能和面積(PPA)帶來全面提升。透過虛擬與實驗製程的結合,我們能確保CFET架構在設計與製造間達到最佳化。」

Hellings進一步指出,雙列CFET架構在邏輯和SRAM單元的設計上,每3.7個場效電晶體僅需一個中間佈線牆即可滿足訊號連接需求,這為未來技術節點的微縮提供了強大支持。

隨著半導體業界逐步進入7埃米及以下節點,元件微縮正面臨物理極限的挑戰,而設計技術協同優化(DTCO)正成為推動技術演進的關鍵工具。imec此次展示的雙列CFET架構,不僅為提升元件密度與性能提供了具體方案,還以其製程創新和可靠性驗證,為CFET在邏輯技術中的量產化鋪平了道路。