於本周举行的2024年国际固态电路会议(ISSCC)上,比利时微电子研究中心(imec)发表了一套类比数位转换器(ADC)的突破性架构,为全新一代的类比数位转换器(ADC)奠定基础。比利时微电子研究中心(imec)所设计的大量时序交错斜率类比数位转换器(ADC)不仅提供高功率效率和极紧凑的尺寸,还可??能支援超凡的高转换速度,所以非常适合用来满足资料中心在资料处理和吞吐量方面的爆炸性需求,这些需求的动力源自云端运算和(生成式)AI应用窜起。

|

| /news/2024/02/22/1637199580S.jpg |

训练AI模型需要大量的运算能力,迫使资料中心去投资建设具备更强算力的光纤网路,这样才能在伺服器、储存装置和网路 设备之间实现快速可靠的通讯。但也因为资料中心的光纤网路需要越跑越快,内部的元件尺寸和功耗也会增加。

作为光纤收发器的关键元件,目前有线传输所用的类比数位转换器(ADC)多半是以(大量的)连续渐进暂存器(SAR)进行时序交错为基础来运作,其特色是会有数十条平行的高速通道。因此,当元件的取样率上升到100GS/s以上时,连续渐进暂存器(SAR)类比数位转换器(ADC)的元件面积会大幅度增加,内连导线也会变长,导致寄生现象加剧,能耗遽增。

为了应付有线传输应用在频宽和资料处理方面供不应求的现象,以及支援对高速类比数位转换器(ADC)的需求,比利时微电子研究中心(imec)提出一套全新的ADC架构来克服这些限制。

imec研究计画主持人Joris Van Driessche表示:「一方面,我们发表的大量时序交错斜率类比数位转换器(ADC)设计是利用慢速但尺寸极小的通道来提升单位面积的转换效率。其次,透过在二维(2D)阵列内部署(大量的)采用这种设计的通道,内连导线的长度就能缩到最短,因寄生现象而散失的功率也会减少,藉此得以实现更隹的功率效率和规模扩充性,同时显着降低ADC的表面积。」

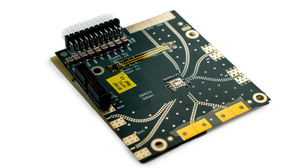

在国际固态电路会议(ISSCC)上,imec为其研发的全新ADC架构发表了一项概念验证,该原型晶片为7位元大量时序交错斜率类比数位转换器(ADC),取样率高达42GS/s。

Joris Van Driessche指出:「就算以42GS/s这样相对中等的取样率来看,我们设计的这套架构带来的效益依然显着。这款晶片以16奈米FinFET技术制造,包含了一个由768颗斜率类比数位转换器(ADC)组成的阵列,核心的晶片面积只有0.07mm2,也就是比传统架构还小了至少两倍。功耗方面也取得新的进展,只有96mW。」 他解释:「换句话说,这也首次证明我们的这套全新架构确实可行。而且随着我们持续提升取样率(达到150GS/s 甚至更高),这套架构所带来的效益只会越来越重要。」

事实上,采用这套架构的5奈米类比数位转换器(ADC)目前已在研发中,且即将完成,目标取样率会高达150GS/s以上,功耗也会降到非常低。与此同时,imec团队也开始探索2奈米设计,锁定250GS/s以上的取样率。

Van Driessche总结:「我们相信这是开发全新一代小尺寸低功耗类比数位转换器(ADC)的重要里程碑,用来支援未来的有线传输应用。这套架构突破了连续渐进暂存器(SAR)类比数位转换器(ADC)的技术限制,当必须进行超高速的讯号转换时,就无需面临缺乏发展动能的风险。」

Imec也邀请更多夥伴加入这项研究,例如专攻有线传输元件开发的无晶圆厂等。此外,有兴趣了解imec类比数位转换器(ADC)智慧财产(IP)的企业也能申请相关授权。