PCI Express (PCIe) 标准组织 PCI-SIG今天宣布,正式推出 CopprLink内部及外部电缆规范。新的CopprLink电缆规范将提供32.0和64.0 GT/s数据传输速率,并采用SNIA的标准连接器外形规格。

|

| /news/2024/05/01/1915524890S.jpg |

PCI-SIG 主席兼会长 Al Yanes 表示,CopprLink电缆规范将 PCIe电缆与 PCIe基本电气规范无缝整合,提供更长的讯号距离和拓扑灵活性。CopprLink电缆旨在与相同的连接器外形规格共同成长,为未来的PCIe技术升级提供扩展性,并满足新兴应用的需求。

另外,Al Yanes 指出,电气工作组已经开始为面向 PCIe 7.0 技术、数据传输速率为 128.0 GT/s 的 CopprLink 电缆进行探索性工作。

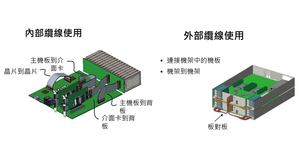

CopprLink 内部电缆规范

· 支援PCIe 5.0 和 6.0 技术,数据传输速率为 32.0 GT/s 和 64.0 GT/s

· 采用 SNIA SFF-TA-1016 连接器外形规格

· 单系统内最长距离为 1 公尺

· 包括主机板到附加卡、主机板到背板、晶片到晶片,以及独立服务器平台节点内的附加卡到背板

· 目标应用包括储存和资料中心运算节点

CopprLink 外部电缆规范

· 支援PCIe 5.0 和 6.0 技术,信号传输速率为 32.0 和 64.0 GT/s

· 采用 SNIA SFF-TA-1032 连接器外形规格

· 机架到机架连接中的最长距离可达2公尺

· 包括 CPU 到储存、CPU 到记忆体、CPU 到加速器,以及分离式服务器平台节点中的加速器架构

· 目标应用包括储存和资料中心AI/ML应用