应用材料公司推出多项创新技术,协助客户运用EUV持续进行2D微缩,并展示业界最完整的次世代3D闸极全环电晶体制造技术组合。

|

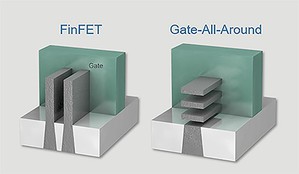

| 继2010年FinFET问世後,闸极全环 (GAA)电晶体将为晶片业带来另一次重大设计转折。创新的材料工程解决方案将提升GAA电晶体的功率和效能。 |

晶片制造商正试图透过两个可相互搭配的途径来增加未来几年的电晶体密度。一种是依循传统摩尔定律的2D微缩技术,使用EUV微影系统与材料工程以缩小线宽。另一种是使用设计技术最隹化 (DTCO) 与3D技术,巧妙地藉由最隹化逻辑单元布局来增加密度,而不需要改变微影间距。第二种方法需要使用晶背电源分配网路与闸极全环 (Gate-All-Around, GAA)电晶体,随着传统2D微缩技术逐渐式微,未来预计能有效提升逻辑单元密度的比率。这些方法能帮助晶片厂商改善次世代逻辑晶片的功率、效能、单位面积、成本与上市时间 (PPACt)。

应用材料公司半导体资深??总裁暨半导体产品事业群总经理帕布·若杰 (Prabu Raja)博士表示:「应用材料公司的策略是成为『PPACt推动公司』(PPACt enablement company),因此今天我们发表的七项创新技术,其目的就是要协助客户运用EUV以持续进行2D微缩。我们也详细说明GAA电晶体的制造方式与今日的FinFET电晶体有何不同,以及应用材料公司备妥为GAA的制造提供业界最完整的产品组合,包括在磊晶、原子层沉积、选择性去除材料的新步骤及两种新整合性材料解决方案 (Integrated Materials SolutionsTM),以产生合适的GAA闸极氧化层与金属闸极。」

延展2D微缩技术

极紫外光 (EUV) 微影技术的出现,让晶片制造商得以实现更小的线宽与更高的电晶体密度。然而,晶片制程不断微缩,使得EUV技术面临重大挑战,因而带动新的沉积、蚀刻与量测技术 (metrology) 需求。

EUV光阻剂显影後,必须透过一连串的中介层(又称为转移层与硬质光罩) 蚀刻晶片图案,才能将图案转移至晶圆上。目前这些薄层都是使用旋转式技术进行沉积,应材今天推出专为EUV设计的Stensar先进图案化薄膜 (Advanced Patterning Film),则是使用应材的Precision化学气相沉积 (CVD) 系统。相较於旋转式沉积技术,应材的CVD薄膜能协助客户调整EUV硬质光罩层的厚度并获得蚀刻弹性,让转移至整个晶圆的EUV图案达到近??完美的均匀度。

应材也详述了Sym3 Y蚀刻系统的特殊功能,能让客户在相同反应室中蚀刻与沉积材料,以改善要蚀刻到晶圆上的EUV图案。Sym3反应室会小心地移除EUV光阻剂,再使用特殊方式重新沉积材料,以减少随机误差所造成的图案偏差。改善後的EUV图案可以提高良率与晶片功率和效能。身为DRAM导体材料蚀刻系统最大供应商,应材的Sym3技术不仅已广泛应用於记忆体,更迅速获得晶圆代工/逻辑制程客户的青睐。

应材也展示了PROVision电子束 (eBeam) 量测技术,可穿透晶片的多层结构,准确量测整个晶圆的EUV图案线宽,帮助客户解决边缘放置 (edge placement) 错误,这是其他量测技术无法做到的。在2021年,应材的电子束系统营收成长了将近一倍,并成为电子束技术第一大供应商。

3D闸极全环 (GAA) 电晶体的工程设计

新兴的GAA电晶体体现了客户如何利用3D设计技术和DTCO布局创新来补强2D微缩,因此即使2D微缩技术式微,仍能快速提高逻辑密度。创新的材料工程解决方案也改善了GAA电晶体的功率和效能。

在FinFET中,形成电晶体电气路径的垂直通道是藉由微影 和蚀刻形成的,这些制程可能导致通道宽度以及通道表面粗糙程度不均匀,进而对功率和效能产生负面的影响,这是除了鳍高的物理限制外,客户转向GAA的主要原因之一。

GAA电晶体类似被旋转了90度的FinFET电晶体,使通道变成水平状而非垂直状。GAA通道是利用磊晶和选择性材料去除技术所形成,这些技术可让客户精确设计宽度和均匀性,以达到最隹的功率和效能。应材推出的第一个产品是磊晶系统,此後即一直是市场领导者。应材在2016年推出Selectra系统时,就开创了选择性材料去除技术的先河,并且是市场的领导者,至今客户使用的反应室已超过1,000个。

制造GAA电晶体的主要挑战之一是,通道之间的空间只有10奈米左右,客户必须在有限的空间内将多层闸极氧化层 (gate oxide) 和金属闸极堆叠沉积在通道的四面。

应材针对闸极氧化层堆叠开发了IMS (Integrated Materials Solution) 系统。更薄的闸极氧化层可以产生更高的驱动电流和电晶体效能。然而,较薄的闸极氧化层通常会导致较高的漏电流 (leakage current),从而浪费功耗并产生热能。应材新的IMS系统将等效氧化厚度缩减1.5埃 (angstrom),使设计者能够在不增加闸极漏电的情况下提高效能,或者在保持效能不变的情况下将闸极漏电减少10倍以上。此系统它将原子层沉积 (ALD)、热处理步骤、电浆处理步骤和量测技术整合在一个高度真空的系统中。

应材还展示了用於GAA金属闸极堆叠工程设计的IMS系统,使客户能够改变闸极厚度,以调整电晶体的??值电压,满足从电池供电的行动装置到高效能伺服器等特殊运算应用的每瓦效能目标。它可在高度真空中执行高精度的金属ALD步骤,实现预防大气污染的目标。