半导体制程微缩已近尾声,尽管研究人员运用超薄SOI、high-k闸极电介质、双闸CMOS、三维FinFET等各种技术,一般认为硅晶CMOS将于2020年微缩至10至7奈米,便真正面临极限。

|

| BigPic:619x435 |

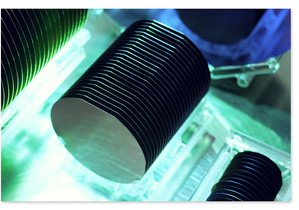

那么,2020年后的半导体产业将会是甚么样貌?除了盖18吋超大晶圆厂、发展3D IC技术外,还有甚么样的可能性?

耶鲁大学电机工程教授及中央研究院院士马佐平博士(T. P. Ma)日前在台湾举行的Sematech年会上,介绍了研究人员试图以碳奈米管(CNT)、石墨烯、III-V族等新材料,做为延续硅晶CMOS未来发展的可行性。而选用这三种材料,主要是因为考虑它们具备更高的迁移率(mobility)特性。

回到基本面,影响CMOS晶体管速度的参数包括信道宽度、长度、电介质、氧化物厚度,以及材料迁移率(mobility)等。近年来,研究人员已透过制程微缩以及导入high-k金属闸等各种创新晶体管架构技术,让摩尔定律能持续进展,并不断提升每个制程节点的效能。

因此,当硅晶微缩达到极限时,若要继续提升晶体管效能,只能求诸新材料,期望以更佳的迁移率,来延续硅晶的未来发展。其中,碳奈米管和石墨烯是近来非常热门的研究题材,2010年的诺贝尔物理奖便是由英国科学将因为找到从石墨中分离出石墨烯的方法而获得。

在这三种新材料中,马佐平博士比较看好III-V族未来扮演的角色,主要是由于,碳奈米管和石墨烯都不易在硅晶圆上生成,而且很难精确控制碳奈米管在晶圆上的放置位置,同时,它们与现有硅晶制程的整合度不高,无法发挥现有硅晶制造基础建设的效益,不容易发展为主流技术。

至于III-V族材料,由于迁移率较佳,它在通讯芯片上的应用已经非常广泛。不过,要开发高迁移率的III-V族MOSFET,仍需找出适当的闸电介质材料,并克服在硅晶上生成III-V材料的问题。此外,III-V材料虽然虽具备较高的电子迁移率,但它的电洞迁移率却较硅晶还低。因此,马佐平提出了单极CMOS架构的概念,全部采用N信道,或许是可行的解决方案。

他强调,有挑战才有机会,就像他的演讲主题「超越硅晶技术的机会与挑战」一样,他说,「我不认为产业会进入后硅晶(post-silicon)时代,而应该是超越硅晶(beyond-silicon)的时代,因为我们将能透过新材料来延续硅晶技术的未来,让这项进入人类文明不过40多年的技术像过去的石器与铜器时代一样,能够源远流长。」

(作者为CTIMES特约主笔)