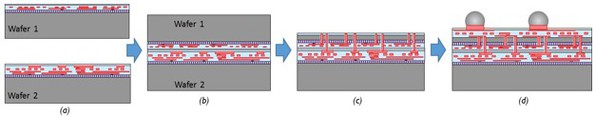

元件封裝技術的創新步伐從未如今日這般高速並且有趣。以往的資訊經是由導線傳送,而近年來,各種3D互連技術在封裝中直接將構件相連接。隨著3D互連密度呈指數級別的增長,線寬需要微縮至5μm或者更低(窄)。然而,目前的3D-SIC(3D堆疊IC)的互連技術並不能支持這樣高的密度。如圖1所示,通過並行的晶圓前段製程,並結合晶圓到晶圓(W2W)接合和極度晶圓薄化步驟,以及採用3D-SOC(3D系統晶片)整合技術方案,則可以讓3D互連密度提升。

| 圖1 : 針對3D-SOC應用的介電層晶圓至晶圓接合的整合方案。圖左至圖右分別為:上下晶圓對準、接合、薄化並進行下一步製程,例如TSV(矽穿孔)的後穿孔蝕刻、穿孔、導線和RDL(線路重佈技術)。 |

|

在極度晶圓薄化製程的探索和開發過程中,文獻[1]和[2]中針對5μm的最終矽(Si)厚度規格,對不同的薄化技術,如研磨、拋光和蝕刻進行了評估。為了比較這些薄化技術,文獻中還定義了作為成功的薄化製程必須遵循的多項標準。首先,跨晶圓的最終Si厚度(FST)必須在一定的限度之內,這樣才可以保證諸如一個穩定的後穿孔蝕刻製程,並且到達正確的導線層。

...

...

| 使用者別 |

新聞閱讀限制 |

文章閱讀限制 |

出版品優惠 |

| 一般訪客 |

10則/每30天 |

5/則/每30天 |

付費下載 |

| VIP會員 |

無限制 |

20則/每30天 |

付費下載 |