在許多嵌入式系統應用中,通常都會使用離散式邏輯元件,例如74'HC系列。這些邏輯元件的優勢在於可以獨立於微控制器(MCU)工作,並且回應速度比軟體快得多。但是,這些元件會增加物料清單(BOM)並且需要占用額外的PCB面積。

為了解決這一問題,Microchip的許多微控制器都整合了一種名為可配置邏輯單元(CLC)的周邊(在PIC MCU上),或名為可配置客製邏輯(CCL)的類似周邊(在AVR MCU上),這兩種周邊都實現了軟體定義的客製邏輯,可以獨立於CPU執行;換句話說,一旦設置了客製邏輯功能,其行為就獨立於微控制器。

但是,這兩種周邊存在限制,即每個實例的邏輯數量非常小。每個CLC大約相當於一個查找表(LUT),而CCL相當於一個內部具有幾個獨立LUT的實例。這兩種周邊的功能非常強大,可用於開發簡單邏輯電路、將各種訊號混合在一起以及與其他硬體周邊相整合。例如,硬體按鈕去抖、WS2812輸出生成和正交解碼這些範例都需要使用這兩種周邊,但微控制器中這兩種周邊的數量並不多,因此限制了應用的複雜度。

為了支援更複雜的應用,PIC16F13145系列微控制器引入一種名為可配置邏輯模組(CLB)的新型邏輯周邊(如圖一所示)。請注意,CLB並不會取代CLC或CCL周邊,元件可以同時配備CLC/CCL和CLB。

PIC16F13145系列微控制器上的CLB包含四個邏輯組,每組包含八個BLE。不同邏輯組的BLE之間彼此連接—每個邏輯組代表兩個GPIO輸出和一個可選的CPU中斷。當工作電壓為5.5V時,BLE的傳播時間典型值小於6 ns。整個結構中的所有BLE共用一個公共時鐘,其時鐘源與可選的時鐘分頻器一起在軟體中進行配置。CLB可以使用微控制器的內部時鐘源之一或外部提供的時鐘源。

該周邊從微控制器的記憶體中進行初始化,之後可透過周邊接腳選擇(PPS)直接從自身結構中控制接腳。用戶可透過PPS重新分配用於硬體周邊的I/O接腳,進而獲得更大的設計靈活性。舉例來說,如果SPI時鐘先前使用RA1,但使用RA6會更有利,那麼便可以透過PPS重新映射接腳。

CLB中的其他元件,包括專用的3位硬體定時器(帶解碼輸出)、用於輸入訊號的邊沿檢測器以及32位元輸出暫存器(用於除錯)。微控制器上的其他核心獨立周邊(CIP)輸出可用作CLB的輸入,以便實現更複雜的設計。

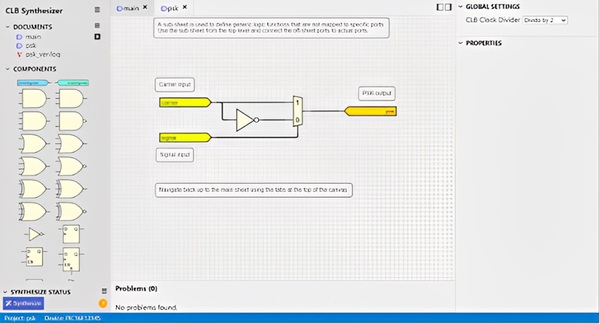

由於CLB比CLC或CCL複雜得多,因此Microchip開發了一款名為CLB合成器的新工具。CLB合成器提供一個用於配置邏輯的圖形介面,如圖二所示。除了邏輯原語之外,該工具還支援更先進的邏輯模組庫(可由用戶預先提供或客製)。

與該圖形工具互動時,後台會自動生成一個Verilog模組用於合成。如果開發人員更喜歡編寫自己的Verilog或者已準備好該文件,則可以將其作為模組直接導入工具。

| 圖二 : 已打開相移鍵控(PSK)範例的CLB合成器 |

|

CLB合成器的輸出是一個組合語言文件,其中包含用於設置CLB的位元流和一些用於將CLB配置為周邊的開源程式碼。該工具可透過MPLAB程式碼配置器(MCC)或獨立在線工具運行。MCC是一款程式碼生成實用程式,允許用戶使用可視化介面來設置和配置微控制器中的周邊。當硬體周邊完成配置後,MCC將生成初始化程式碼和元件API。

在運行時,使用板上硬體直接從程式記憶體加載CLB位元流。這種實現的好處在於如果在程式運行時需要更改CLB配置,則可以使用儲存在元件記憶體中的不同位元流重複執行加載過程。

為了展示CLB的應用創建一系列應用範例。在此將討論兩個範例:7段顯示轉換器和SPI至WS2812轉換器,應用範例可作為構件複製以用作完整解決方案的一部分。主旨在於展示該周邊的實用性以及它能夠為設計帶來哪些價值。

第一個應用案例是7段顯示轉換器。7段顯示器可透過一組普通的I/O接腳驅動,但標準實現通常需要使用軟體定義的查找表,將輸入數位轉換為適合顯示器的正確輸出模式。在該實現中,CLB充當硬體查找表。所需的輸出字符(0到F)從軟體加載到CLB輸入暫存器中。顯示器的每個輸出段均由LUT控制,以將輸入映射到輸出。

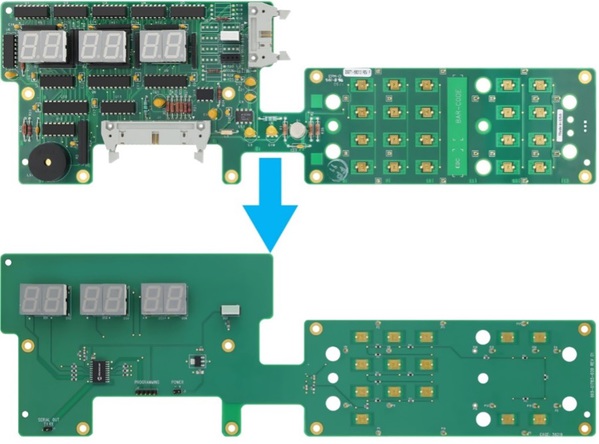

該應用範例在內部用於構建計時系統的新控制板。最初的用戶介面是在20世紀80年代使用74'HC系列邏輯開發。使用CLB後,一個20接腳的微控制器即可實現電路板上的顯示和鍵盤邏輯,極大化精簡了物料清單(BOM)。圖三並排給出了兩種方案以供比較。

| 圖三 : 原PCB與新PCB的並排比較。該範例由Josh Booth開發。 |

|

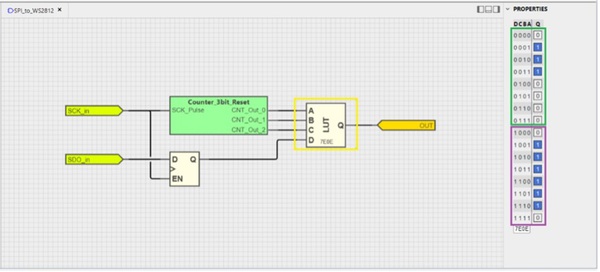

下一個範例是SPI至WS2812轉換器。WS2812是一種單線串列協議,用於透過脈寬調製控制LED陣列。在本例中,SPI硬體用作要發送到LED的資料的移位暫存器,而CLB用於將SCLK和SDO轉換為預期的輸出。

在本範例中,這是透過單觸發3位計數器、帶使能功能的D鎖存器(D-latch)和4輸入LUT來實現,如圖四所示。該實現的技巧體現在SPI和CLB的時鐘源。SPI時鐘設置為空閒高電位、在上升沿改變狀態並以WS2812輸出的頻率(800 kHz)運行,而CLB的時鐘源以前者10倍的頻率(8 MHz)運行。當SCLK為低電位時,將觸發3位計數器並開始計數。當計數到7(0b111)時,3位計數器將停止並保持為0,直到時鐘脈衝的下一個低電位週期為止。

計數器的輸出與輸出資料的鎖存版本一起饋入4輸入LUT。這將設置資料的輸出模式,如圖四的右側所示。計數器復位後,計數器輸出將保持為0以完成循環。之後,可根據需要發送SPI硬體中的下一個字節,重複該循環。

| 圖四 : SPI至WS2812轉換器框圖(由Petre Teodor-Emilian開發) |

|

這兩個範例都證明了微控制器內部離散邏輯的優勢。硬體周邊可將CPU從各種任務中解放出來,進而縮短回應時間並降低功耗,同時減少元件數量。有了CLB,之前無法在微控制器內部實現的複雜應用現在都可以順利開發。目前,可透過PIC16F13145系列微控制器來獲取CLB。

(本文作者Robert Perkel為Microchip Technology 8位元微控制器業務部應用工程師)