隨著嵌入式應用漸趨複雜,硬體架構與嵌入式系統設計工具也必須有所改良,才能因應各種嚴苛需求,同時縮短設計時間。許多傳統的嵌入式系統必須配備單一 CPU,因此系統設計工程師得提高 CPU 的時脈速度、改用多核心運算技術,同時透過創新,才能滿足複雜應用所需的運算效能。

然而,越來越多的系統設計工程師選用了具有多種不同處理元件的異質運算架構,以便在效能、彈性、成本、延遲時間與其他要素之間取得最佳平衡。這樣一來即可因應新一代嵌入式系統的設計需求。

系統中的異質架構

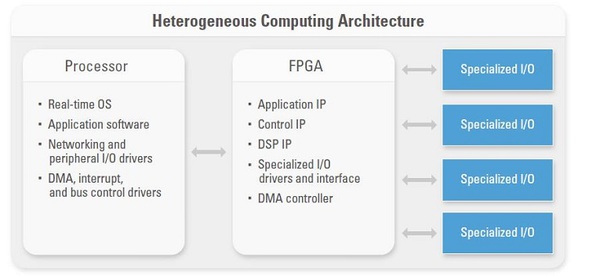

如要了解異質運算架構的優勢,請想像一個由 CPU、FPGA、I/O 所組成的架構。FPGA 可說是平行運算的理想選擇,可透過許多平行資料通道來處理訊號。此外,由於 FPGA 會直接在硬體內執行運算作業,因此可縮短客制化觸發與高速閉迴路控制等作業的延遲時間。

再者,將 FPGA 整合至運算架構後還可以加強嵌入式系統的彈性,比固定邏輯的系統更容易升級,也可隨時因應不同的 I/O 需求。只要在同一個異質架構內整合 CPU 與 FPGA,系統設計工程師就可以同時享有 FPGA 與 CPU 所帶來的優勢,堪稱魚與熊掌兼得。

此外,假如單元件解決方案並不適合某項應用,那還不如採用異質架構來得乾脆。舉例來說,使用單一 FPGA 來處理低延遲時間的平行工作,其功效可能等同於採用多個 CPU 的成效。

配備多個處理元件的嵌入式系統設計可提供多重優勢,但也可能引起軟體開發的相關問題。因為處理元件各有各的特殊架構,而且設定作業需要不同的工具組合與專業技巧,所以設計團隊的規模不容小覷。

比如說,FPGA 設定通常需要 VHDL 程式設計的相關知識,這又會需要更多員工、大量的培訓投資,以及更昂貴的外包成本。此外,為了支援異質架構而開發軟體環境所需的心力也相當可觀,包含驅動程式整合、介面卡支援、銜接元件所需的中介軟體、I/O 介面邏輯等多不勝數。

系統設計工程師可透過整合式的軟硬體平台來解決問題,此平台由標準的異質架構、可互換 I/O、高階系統設計軟體所組成。高階設計工具採用基礎硬體的相關知識,可簡化系統架構與 I/O 的開發流程,提高生產力之餘,還可以降低繁瑣的實作管理需求。採用異質架構開發嵌入式系統時,高階系統設計工具有助於簡化個別運算元件的架構 ( 例如 FPGA),還可提供一致的設定模型,方便工程師在設計嵌入式系統時處理不同的元件並享有其優勢。

此外,高階設計軟體的抽象化功能可簡要說明有效的運作方式,提高程式碼的重複使用率,無論硬體或通訊介面如何改變都沒問題。

| 圖一 : 在異質運算架構中整合微處理器與 FPGA 後,嵌入式系統設計工程師即可發揮每個運算元件的優勢,同時有效滿足複雜的應用需求。 |

|

LabVIEW 可重設 I/O (RIO) 架構

目前採用異質架構的現成嵌入式系統平台已相當普遍,此平台可降低客制化硬體的設計需求。以 NI LabVIEW RIO 架構為例,當中結合了 LabVIEW 系統設計軟體與 NI RIO 硬體 (採用處理器、FPGA 與模組化I/O),並且提供各式各樣的機型與效能選項,包含機板層級的 NI Single-Board RIO 與工業級的 NI CompactRIO 及 PXI。

豐富的 I/O 模組生態系統包含 比與數位量測、工業級匯流排連接選項與其他產品和功能,皆可協助工程師將此平台用於各種領域,包含電力電子控制與醫療成像。

實用的異質運算技術

嵌入式系統設計的異質架構概念深深影響了許多產業。舉例來說,Thales UK 這家交通運輸解決方案公司採用 LabVIEW 與 CompactRIO,針對虛擬測試火車設計出一種自動化傳訊系統。這項傳訊計畫的目標在於提高 33% 的系統容量 ( 等於每小時多容納 5,000 名乘客),同時縮短 22% 的旅程時間。為了模擬實際的客運列車並測試鐵道狀況,Thales UK 團隊選用 FPGA 搭配嵌入式處理器,以透過單一系統提供高速控制、資料擷取、資料分析等功能。

該公司使用現成的 CompactRIO 硬體與 LabVIEW,打造出完整的監控系統,不但可以模擬實際火車的訊號,還可以量測測試資料、記錄資訊以便後續審查。Thales UK 不僅改革了傳統的測試方法,同時把測試時間從好幾天縮短為數小時。而且只要大約一半的人力即可執行全新的虛擬火車測試作業。

| 圖二 : Thales UK 的工程師採用 CompactRIO 與 LabVIEW,模擬出倫敦地下鐵路網的客運火車 |

|

Thales UK 的設計團隊皆採用異質運算架構,打造出創新的高效能嵌入式系統。由此可知,只要有現成硬體與高階的系統設計工具,小型團隊與該領域專家即可充分運用這些架構所帶來的優勢,不必建置客制化硬體,也不用學習多種特定的設計工具,更不需要像以傳統方式設定多種處理元件那麼麻煩。

由於異質架構對嵌入式系統設計來說越來越重要,各組織與團隊都可從中獲得包含優異的功能、成效與彈性等好處。