imec展示全球首次實驗示範採用18nm導線間距的雙金屬層半鑲嵌模組,強調窄間距自對準通孔的重要性,同時分析並公開該模組的關鍵性能參數,包含通孔與導線的電阻與可靠度。

銅雙鑲嵌製程在業界長跑20餘載,能夠穩定量產具備高可靠度的晶片內部導線。然而,隨著元件面積持續緊縮,金屬導線間距降至20nm以下,後段製程的電阻與電容(RC)因而大幅增加,加劇了電路傳輸延遲的問題。這就迫使相關產研單位去開發替代的整合方案與金屬材料,優化窄間距金屬導線的性能。

imec約在5年前首次提出半鑲嵌製程的概念,作為替代銅雙鑲嵌製程的可行方案,用於1nm製程及其後續製程節點,整合不同金屬層間的局部導線,實現互連。

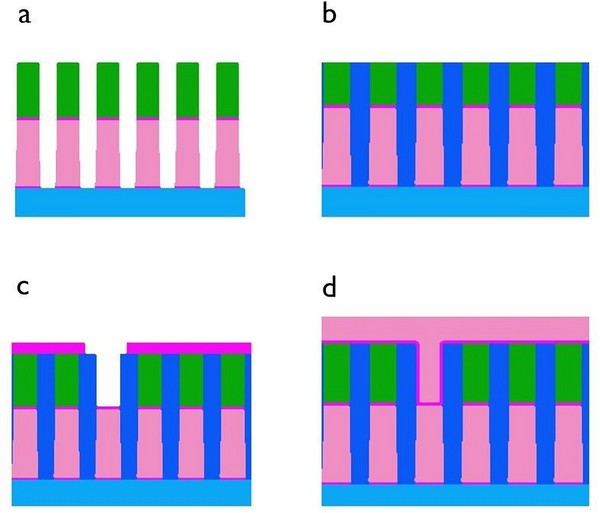

| 圖一 : imec半鑲嵌製程流程(a)釕蝕刻,生成底部元件層的局部金屬導線(Mx)(b)空隙填充(c)通孔蝕刻(d)通孔填充與生成金屬層之上(Mx+1)的頂部元件層。 |

|

不同於雙鑲嵌製程,半鑲嵌整合技術以直接圖形化的方式製造內部金屬導線,這也稱作減法導線製程(subtractive metallization),亦即蝕刻,過程中金屬導線不需經過化學機械研磨(CMP)。負責連接不同導線層的通孔採用單鑲嵌製程製造,隨後以金屬填滿後繼續填充,也就是說持續沉積金屬材料,直到介電層上方生成一層金屬層。該金屬層接著進行微影蝕刻,以製成第二層導線層,形成一條垂直的互連導線。完成金屬導線的圖形後,元件層上的空隙可以用介電材料填充,或是當作局部元件層的(局部)氣隙(airgap)結構。

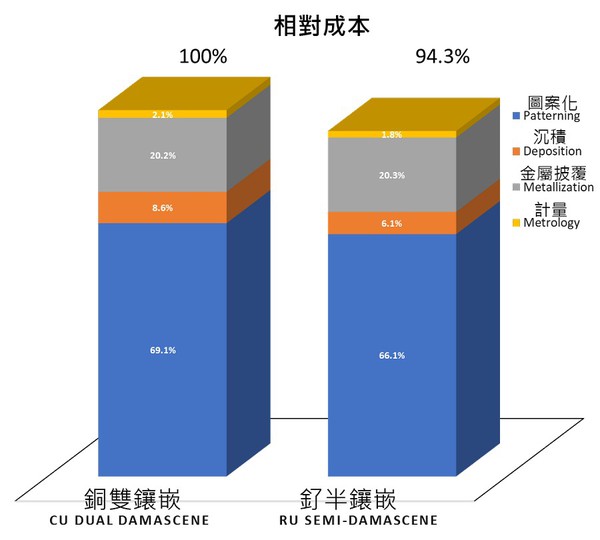

值得注意的是,在半鑲嵌製程中,通孔與頂部金屬層會同步製造,與傳統的雙鑲嵌製程相同。因此,相較之下,半鑲嵌製程更有效率,具備低成本的競爭優勢(見圖二)。

| 圖二 : 比較半鑲嵌與雙鑲嵌製程在製造金屬導線間距18nm元件時的成本結構。 |

|

半鑲嵌製程的優勢

在製造窄間距金屬導線時,半鑲嵌製程具備幾項優勢,勝過雙鑲嵌製程。imec研究員暨奈米導線研究計畫主持人Zsolt Tokei表示:「第一,半鑲嵌製程能製造高深寬比的導線結構,同時控制電路的電容,有利於降低整體的RC延遲。第二,可以省去金屬導線的化學機械研磨步驟,實現簡便且低成本的整合方案。第三,半鑲嵌製程需要可圖形化又不需阻障層的金屬材料,例如鎢(W)、鉬(Mo)或釕(Ru)。與銅鑲嵌不同,採用這些金屬材料不需要金屬阻障層,如此一來,金屬導線可以充分利用珍貴的導電區域,在微縮設計中展現優異的通孔電阻值。」

當然,除了這些優勢,半鑲嵌製程在獲得業界採用前,仍有幾項技術挑戰必須解決。其中一站必經之路就是實際演練兩層金屬層之間的導線互連。雖然目前只能透過模擬建模來計算性能參數,imec近期首次展示了雙金屬層半鑲嵌模組的實驗數據。

製程關鍵:全自對準通孔(fully self-aligned via)

在金屬導線間距僅有20nm的情況下,半鑲嵌製程的成功關鍵在於通孔蝕刻的精準度,必須恰好在狹窄導線的上方。倘若元件頂層與底層的通孔與導線未能對準,通孔與緊鄰的導線之間就可能產生漏電流。這些漏電路徑的產生源自傳統圖形化技術在製造微縮尺寸的通孔結構時的對準誤差過大。

imec技術研究主任Gayle Murdoch表示:「製出性能完備又能全自動對準的通孔,一直是半鑲嵌製程夢寐以求的技術。imec內部負責整合、微影、蝕刻與清洗技術研究的團隊之間緊密合作,共同立下此次里程碑。利用我們開發的全自對準整合方案,通孔對準誤差可以校正補償的幅度高達5nm,成果斐然。」

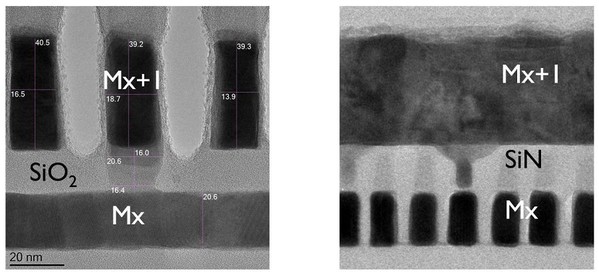

| 圖三 : 自對準通孔沿著金屬層(左)與橫跨金屬層(右)結構拍攝的穿透式電子顯微鏡截面影像(X-TEM),顯示自對準通孔可以準確落在18nm間距的釕導線上方。 |

|

在填充空隙後,可以透過移除局部的氮化矽(SiN)來確保底部元件層的通孔能夠自行對準下方的導線圖形。頂部金屬層(釕)的自對準通孔則利用過度蝕刻(over-etch)實現,在通孔過度填充並進行釕金屬圖形化後,持續蝕刻出通孔圖形。

全球首例18nm導線間距半鑲嵌製程

利用減法製造對釕金屬進行蝕刻,並導入自對準通孔設計,最終能製出導線間距18nm的雙金屬層元件。底部釕金屬層(Mx)的導線寬度9nm,利用極紫外光微影(EUV)與自對準雙重圖形化(self-aligned double patterning;SADP)技術製造,金屬層上方的頂層元件層(Mx+1)與通孔則採用單次曝光EUV製程。頂層導線還會搭配氣隙結構,抵銷電容增加對性能的影響。

在比較釕與銅的導線電阻與導電面積時,可以發現釕在採用目標導線間距設計時的性能勝過銅。通孔的自對準性能也經過數學形象學與電學確認。研究結果顯示,通孔電阻表現優異,導線間距為26nm~18nm時,可以控制在40?~60?的範圍,通孔與導線之間的崩潰電場則是小於9MV/cm。

Zsolt Tokei表示:「我們經過研究顯示,半鑲嵌製程在所有的關鍵性能參數方面呈現絕佳表現,包含通孔與導線的電阻與可靠度。此次實驗結果表示,半鑲嵌製程能夠代替雙鑲嵌製程,用於1nm製程或後續製程節點,整合前三層的局部導線層。此次我們開發的雙金屬層元件導入自對準通孔技術,證實是半鑲嵌製程的關鍵。」

未來可以透過增加導線的深寬比(降低電阻),同時維持氣隙結構(控制電容)來提升元件性能。與此同時,imec對中段與後段製程也有明確想法,能導入製程方案來推動半鑲嵌製程進一步發展,進而從標準元件層級縮小元件尺寸。

(本文由imec提供;編譯/吳雅婷)