根據SEMI國際半導體產業協會公布的全球晶圓廠預測報告(World Fab Forecast)中指出,晶片需求不斷上升帶動全球半導體晶圓廠產能持續成長,2024年及2025年預計將各增加6%及7%,月產能達到創紀錄的3,370萬片晶圓歷史新高。

全球晶圓廠產能持續攀升

5奈米以下製程在資料中心訓練、推論和領先製程裝置生成式AI人工智慧技術的助力下,2024年可望成長13%。另為提高晶片能效,英特爾、三星和台積電等晶片大廠準備在明年開始生產 2奈米全環繞柵極(gate-all-around;GAA)晶片,也將讓2025年領先製程總產能出現17%的漲幅。

SEMI全球行銷長暨台灣區總裁曹世綸分析,從雲端運算到各種邊緣裝置,AI 處理無所不在,讓高效能晶片開發競逐更加白熱化,帶動全球半導體製造產能的強勁擴張,可說創造了一個正向循環:AI加速各式應用中半導體的成長,將激勵進一步的投資。

中國晶片製造商可望維持兩位數產能成長,預計2024年增幅15%達每月885萬片,2025年再成長14%來到每月1,010萬片,幾乎佔業界總量三分之一強。儘管過度擴張的潛在風險,為了舒緩近期出口管制帶來的影響及其他原因,中國仍積極投資推動產能擴張,包括華虹集團(Huahong)、晶合集成(Nexchip)、芯恩(Sien Integrated)和中芯(SMIC)等代工大廠以及 DRAM 製造商長鑫存儲都持續加強投資力道,提升中國區半導體產能。

其他主要晶片製造地區至2025年產能成長預估均不超過5%。台灣以月產580 萬片(成長4%)居第二;南韓可望繼2024年首度突破月500萬片後2025年再漲7%來到540萬片排第三位;日本、美洲、歐洲與中東及東南亞半導體產能分別為月產470萬片(年增3%)、320萬片(年增 5%)、270萬片(年增 4%)和180萬片(年增 4%)。

受惠於英特爾設立晶圓代工服務以及中國產能擴張,晶圓代工部門2024年產能將成長11%,2025年也保有10%的漲幅,預計至2026年將達月產1,270萬片的規模。

此外,工研院也認為,半導體市場受惠於AI議題帶動相關供應鏈需求強勁,將樂觀看待全年成長率可達到17.7%,預估半導體產值將首次突破NT.5兆元大關的5兆1,134億元。隨著萬物皆AI(AI for all)時代來臨,台灣憑藉半導體、伺服器、記憶體和其他ICT產業的國際競爭優勢,未來發展可期。

同時預估2024年AI發展將從雲端走向終端,AI PC與AI手機將成為GAI普及的關鍵應用,其對於高效能的需求也推動半導體封裝技術朝高密度互連發展。台灣半導體產業應趁機佈局相關技術與產品,即除了2.5D/3DIC等封裝技術外,也在成本與效能的優勢下,驅動扇出型封裝延伸至面板級載體;並透過強化晶片異質整合與高階封裝技術,以滿足裝置端AI的終端高效能應用。

半導體產業關鍵趨勢

當前半導體產業的趨勢主要受到生成式AI、高效能運算(HPC)、以及新興應用的推動。生成式AI應用的崛起讓半導體產業熱度再度上升。這些應用需要大量的運算能力,推動了對先進製程和晶圓代工產能的需求。隨著市場需求的增加,全球晶圓廠的建設和設備投資預期在2025和2026年創下新高。台灣仍將維持全球第二大半導體產能排名,並且預計自2024年起將有5座新晶圓廠投產。

未來半導體市場的成長動能將仰賴新興應用的刺激,特別是AI、新能源與智慧聯網。AI伺服器與電動車有機會在2027年達到倍數成長,成為推動半導體成長的主力。而半導體供應鏈面臨高度競合,特別是在美中對抗與地緣政治風險的影響下,全球經貿出現了碎片化的情況。這些不確定因素對半導體產業的影響巨大,需要企業保留充分彈性資源以應對外部環境變化風險。隨著半導體產業的發展,永續發展和資安風險也成為重要議題。企業需要在技術創新與環境保護之間取得平衡,並加強對半導體資安風險的防範。

奈米片

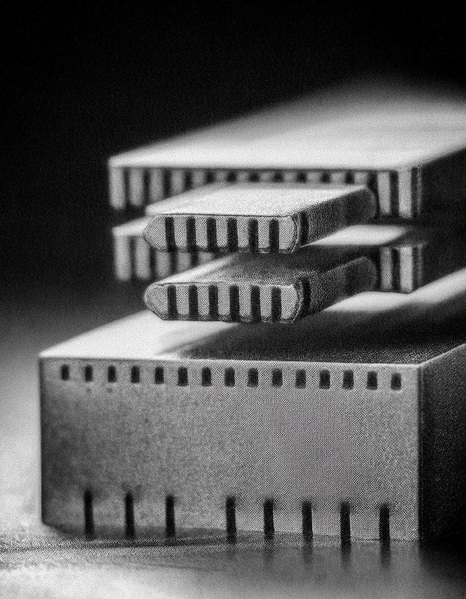

奈米片可以提升晶片性能,並增加晶片上的電晶體數量,使晶片變得更小、更快、更可靠、更具效率。

在半導體產業加速發展的今日,我們特別需要關注最新半導體技術的發展動向。奈米片(Nanosheets)就是在半導體發展中,一個受到關注的新話題。奈米片可以顯著提升晶片的性能和能效,並增加每個晶片上的電晶體數量,使晶片變得更小、更快、更可靠、更具效率。奈米片的製程技術可以視為半導體製造中的一個重要進展。

| 圖二 : Nanosheet是一種3D結構電晶體。此為示意圖,非真實影像。 |

|

奈米片電晶體(Nanosheet Transistor)是一種先進的場效電晶體技術,具有更高的效能和更低的功耗。這種技術利用奈米片作為通道材料,能夠提供更好的電流控制和更高的開關切換速度。這對於提升處理器設計人員的選擇,尤其是在人工智慧、雲計算等前沿工作負載的功能上,有著重要意義。目前台積電的A16製程技術結合了奈米片電晶體及創新的背面電軌解決方案,大幅提升邏輯密度及效能,預計於2026年量產。這些技術進步將推動半導體產業的發展,滿足不斷成長的需求。

奈米片晶體管的製造過程涉及多個步驟,首先選擇適當的材料,例如矽(Si)或鍺(Ge),並準備好晶圓。透過光刻技術在晶圓上定義出奈米片的圖案。這包括塗覆光阻劑、曝光和顯影等步驟。蝕刻技術可以去除不需要的材料,形成奈米片的結構,例如乾蝕刻和濕蝕刻。在奈米片上沉積閘極材料,並進行圖案化以形成閘極結構,通常包括高介電常數材料和金屬閘極。接著是離子注入和退火程序,以在奈米片的兩端形成源極和汲極。最後,將奈米片晶體管與其他元件互連,並進行封裝以保護晶片。這些步驟需要高度精密的設備和技術,以確保奈米片晶體管的性能和可靠性。

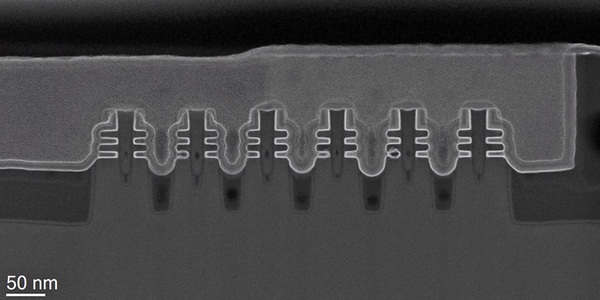

奈米片技術在半導體領域中展現出巨大的潛力,成為下一代晶體管技術的關鍵。奈米片晶體管相比傳統的FinFETs和全包圍式納米線晶體管(Gate-All-Around Nanowire Transistors),具有更小的尺寸、更高的驅動電流和更低的功耗。這些特性使得奈米片技術在提升元件性能和能效方面具有顯著優勢。

奈米片技術的性能表現令人矚目。與目前最先進的7nm FinFET技術相比,奈米片技術在相同功耗下可提升超過25%的性能,並在相同性能下節省超過50%的功耗。此外,奈米片晶體管還具有優越的電氣特性,包括更好的短通道控制和更小的閾值電壓變異(Vth)。

在製造奈米片晶體管的過程中,有幾個主要挑戰和限制需要克服。由於奈米片的尺寸非常小,精確的圖案化和蝕刻變得極為困難。高縱橫比的垂直結構需要非常精密的技術來進行圖案化和蝕刻。而多層堆疊結構的熱退火過程也是一個挑戰。半導體材料在晶體生長和製造過程中可能會出現結構缺陷,熱退火可以修復這些缺陷,但需要精確控制溫度和時間。

另外,選擇合適的材料來製造奈米片晶體管也是一個挑戰。材料的電氣特性、熱穩定性和機械強度都需要仔細考慮。而隨著晶體管尺寸的縮小,短通道效應變得更加顯著,這會影響晶體管的性能和穩定性。需要創新設計來減少這些效應。

台積電2奈米製程

台積電的2奈米(N2)技術開發依照計劃進行並且有良好的進展。N2技術採用第一代奈米片(Nanosheet)電晶體技術,提供全製程節點的效能及功耗進步。主要客戶已完成2奈米矽智財設計,並開始進行驗證。台積電並發展低阻值重置導線層、超高效能金屬層間電容以持續進行2奈米製程技術效能提升。

N2技術預計於2025年開始量產,並將成為密度和能源效率上最為先進的半導體技術。台積電N2技術採用奈米片電晶體結構,其效能及功耗效率皆提升一個世代,以滿足節能運算日益增加的需求。目前已經有主要客戶完成了2奈米IP設計並開始進行驗證

| 圖三 : Nanosheet有兩個片狀式閘極。(source:imec) |

|

台積電A16製程技術

台積電的A16製程技術是2奈米的進化版,結合了奈米片電晶體及創新的背面電軌解決方案,大幅提升邏輯密度及效能。A16是下一代的奈米片(Nanosheet)電晶體技術,並採用超級電軌技術(Super Power Rail;SPR)。台積公司的SPR是具有獨創性的背面供電解決方案。SPR將供電線路移到晶圓背面,以在晶圓正面釋放出更多訊號線路佈局空間,來提升邏輯密度和效能。SPR也能大幅度降低IR drop,進而提升供電效率。更重要的是,透過backside contact技術能夠維持與傳統正面供電下相同的閘極密度(Gate Density)、布局版框尺寸(Layout Footprint)和元件寬度調節的彈性,因此可以提供最佳的密度和速度上的優勢。

A16特別適用於具有複雜訊號線路和高密度供電線路的高效能運算(HPC)產品。相對於N2P,A16在相同電壓下可得到8%~10%的速度提升,或在相同速度下減少15%~20%的功耗,並提升1.07~1.10X的晶片密度(Chip Density)。這項技術預計於2026年量產。

結語

奈米片技術在半導體領域中具有重要的發展意義,並且在持續推動摩爾定律的進一步發展中扮演著關鍵角色。儘管在製造過程中,奈米片技術面臨著圖案化與蝕刻、熱處理、材料選擇和短通道效應等挑戰。然而,透過先進的技術和創新,這些挑戰正在逐步被克服。

奈米片晶體管的製造過程,包括材料選擇與準備、光刻技術、蝕刻、閘極堆疊、源極與汲極工程,以及互連與封裝等步驟。隨著技術的不斷進步,奈米片晶體管可望成為未來電子設備的核心元件,推動科技的進一步發展。