在迎來高數值孔徑極紫外光(high-NA EUV)微影時代之際,比利時微電子研究中心(imec)運算技術及系統/運算系統微縮研究計畫的資深副總裁(SVP)Steven Scheer探討imec與艾司摩爾(ASML)合建的High-NA EUV微影實驗室對半導體業的重要性。

由ASML與imec聯手在荷蘭費爾德霍溫建立的微影實驗室正式啟用,為推動High-NA EUV技術邁向量產立下了里程碑。記憶體和邏輯晶片的頂尖製造商現在可以使用首款0.55NA高數值孔徑(high-NA)EUV曝光原型機TWINSCAN EXE:5000及周邊基礎設施,包含塗佈及顯影機、量測工具、晶圓及光罩處理系統。在IDM及晶圓代工廠的晶圓廠房開始運作這些微影機台之前,imec與ASML將協助他們降低這項圖形化技術的開發風險,並支援他們開發專有的High-NA EUV應用案例。

實驗室未來也會開放給更廣泛的供應商生態系統來使用。實驗室的顯影設施將能讓他們在High-NA EUV專用材料與設備的工程設計領域成為先鋒。實驗室的第三類使用者則是imec及其先進圖形化研究計畫的幾位夥伴,該計畫推動圖形化生態系統朝向High-NA EUV的未來技術世代發展。

比利時微電子研究中心(imec)運算技術及系統/運算系統微縮研究計畫的資深副總裁(SVP)Steven Scheer表示,這間位於荷蘭費爾德霍溫的High-NA EUV微影聯合實驗室的成立目標是加速High-NA EUV技術量產並提升其成本效益。ASML與蔡司(ZEISS)在短時間內已經成功開發high-NA EUV曝光機的專用解決方案,這些方案與曝光源、光學元件、鏡頭變形、光罩場域拼接、縮短焦點深度(DOF)、邊界放置誤差及疊對準確性有關。

同時,imec攜手ASML及我們的廣泛供應商網絡密切合作,共同籌備0.55NA圖形化生態系統—如同imec在2024年國際光電工程學會(SPIE)先進微影成形技術會議(Advanced Lithography and Patterning Conference)所公佈的消息。確保了用於第一代High-NA EUV的先進光阻劑、塗佈底層材料、光罩、量測技術、(變形)成像策略、光學鄰近修正(OPC)與整合圖形化及蝕刻技術都能如期供應。

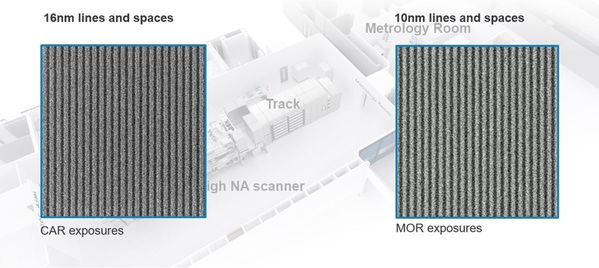

這些籌備工作在近期促成了首批晶圓的曝光,寬度為10奈米和16奈米的導線/間隔(space)—即間距(pitch)為20奈米和32奈米,分別能在金屬氧化物阻劑(MOR)與化學放大阻劑(CAR)曝光後印刷出圖形。目前曝光原型機與基礎建設已經就緒,預計在2025-2026年將會導入量產。

| 圖一 : 由imec與ASML合建的High NA實驗室所用的High-NA EUV曝光機EXE:5000展示一次曝光後所取得的16奈米寬導線圖形,以及首次實現10奈米寬的導線圖形。 |

|

首例應用: 14A邏輯晶片與D0a動態隨機存取記憶體(DRAM)

Steven Scheer表示:「High NA EUV的首例應用會是14A(埃米)世代邏輯晶片的量產,該技術節點將會以單次曝光完成24奈米間距的金屬導線/間隔(M0/M2層)圖形化,甚至最終微縮到18奈米間距。相較於現有的多重圖形化0.33NA EUV製程,0.55NA單次曝光將能提高產率和縮短週期時間,甚至可能減少二氧化碳排放量。最終,這項技術會成為互補式場效電晶體(CFET)晶片的關鍵技術,為這種晶片的特殊複雜結構生產圖形。

記憶體的晶片製造則會隨後導入這項技術,用來生產動態隨機存取記憶體(DRAM)的最關鍵元件結構。High-NA EUV技術估計將能透過單次曝光來生產電荷儲存節點連接墊(storage node landing pad)與位元線周邊的圖形。2D動態隨機存取記憶體(DRAM)的D0a技術世代會是第一個應用契機,所需的中心間距為28奈米。」

邁向High-NA EUV的未來技術世代

Steven Scheer指出:「儘管先進半導體生態系統的目標是在短期內把High-NA EUV技術引進量產,但是imec及其夥伴看得更為長遠,聚焦在實現High-NA EUV的未來技術世代。為了這些研發活動,由imec與ASML合建的High-NA EUV微影實驗室將作為imec設施的虛擬延伸。雖然曝光會在荷蘭費爾德霍溫進行,但是前處理與後處理的部分工作仍將在imec的12吋晶圓無塵室進行。

首先,我們會密切監測High-NA EUV微影束型(cluster)原型機的性能—束型機即相連的曝光機與顯影機。為此,imec目前持續在製備專用的晶圓堆疊,基線製程也正在轉移到High-NA EUV束型原型機上。我們的團隊將會評估束型機的最高解析度(最終目標是實現導線/間隔的金屬間距為18奈米、接觸孔洞間距為28奈米)、穩定性(例如經過曝光後的關鍵尺寸穩定度與結構缺陷密度)以及有效焦點深度(DOF)。因為這種機台的數值孔徑更高,其焦點深度(DOF)預計會比0.33NA EUV設備還要小兩到三倍,這也是0.55NA EUV設備所用的光阻薄膜更薄的原因之一。

此外,我們也攜手量測領域的夥伴,目前已經在這間聯合實驗室開發及安裝專用的檢測工具,用來監測與改善圖形化結構的表面缺陷。一直以來,電子束檢測都被選為研究超小型接觸孔洞表面缺陷的主要工具。我們希望能實現業界的遠大目標:每測量一百萬個接觸孔洞時,把每個接觸孔洞的缺陷數量控制在只有一個。在金屬導線/間隔方面,光學檢測工具則與電子束整合,以偵測和分類缺陷,並引導實現每立方公分只有不到一個缺陷的目標。

最後,邏輯與DRAM應用案例也正在醞釀。較大型的製程模組未來會針對圖形化解析度與表面缺陷進行檢查,採用例如檢測工具與電氣測試的組合。」

擴展O.33NA EUV業務 促使高低數值孔徑雙獲益

Steven Scheer表示:「在我們的無塵室,最新一代的0.33NA EUV曝光機仍是用來協助優化新世代High-NA EUV圖形化生態系統的輔助工具組。另外,並非所有的晶片特徵都需要High-NA EUV技術—試想元件中間與全域的晶片內連導線,因此,我們也持續改良0.33NA EUV生態系統。除此之外,0.33NA與0.55NA曝光技術還有一些常見的挑戰,像是對改良版光阻劑的需求。」

「0.333NA擴充業務」的重點領域之一是用於High NA EUV的光罩場域拼接技術。我們之所以需要光罩場域拼接技術是因為導入了變形鏡片(即一種X軸與Y軸的縮小倍率不同的鏡片),加上使用的空白光罩尺寸固定不變(使得場域只有晶圓面積的一半)

。imec在2024年國際光電工程學會(SPIE)先進微影成形技術會議(Advanced Lithography and Patterning Conference)分享了對於實現光罩解析度場域拼接技術的最新見解,這項技術在面對場域尺寸縮小的情況時能減少更動設計的需求。這項研究利用imec無塵室內的NXE:3400C曝光機完成,並與ASML與光罩夥伴合作進行。

另一個關鍵議題是光阻劑和塗佈底層顯影。imec攜手光我們的阻供應商,目前正在篩選替代的光阻材料,並根據表面缺陷、粗糙度與阻劑減量來衡量這些材料的表現。化學放大阻劑(CAR)已經在光學微影領域縱橫數十年,未來也會持續在選定的應用案例佔有優勢。然而,High-NA EUV可能會顛覆金屬氧化物阻劑(MOR)的發展,這種光阻劑在高解析度導線/間隔與小型六方柱結構的方面一直展現良好的微影性能。為瞭解這些金屬氧化物阻劑如何與極紫外光線發生作用而進行基礎調查將能讓我們克服現存的挑戰,例如這些光阻劑的性能穩定度。我們也會研究與這些光阻劑匹配的塗佈底層,以提升其附著力。此外,選配塗佈底層和光阻材料的組合還能有機會進一步減少曝光阻劑,進而降低(High-NA)EUV的曝光成本。

最後,鎖定定向自組裝技術(DSA),該技術利用嵌段共聚物(BCP)的微相分離現象來定義圖形。業界目前對於採用DSA並搭配EUV的做法已經產生興趣,因為這麼一來可以降低表面粗糙度、修復缺陷及降低EUV阻劑。目標是進一步減少DSA圖形的表面缺陷。更長遠來看,我們會持續為了落實High-NA EUV來開發DSA技術。為了應用於High-NA EUV製程,我們未來勢必要把DSA圖形的間距微縮到24奈米以下。目前所用的聚苯乙烯-b-甲基丙烯酸甲酯(PS-b-PMMA)型嵌段共聚物(BCP)無法做到這點,所以攜手DSA材料供應商,共同著手研究所謂分子作用力較高的c嵌段共聚物。

Hyper-NA EUV:光刻技術的明日之星?

Steven Scheer表示:「雖然現在把超高數值孔徑紫外外光(Hyper-NA EUV)稱作明日之星,著實言之過早,但是imec與ASML已經開始進行相關的可行性研究。Hyper-NA的數值孔徑可以高達0.75-0.85,可能成為接續0.55NA EUV的下一代技術,業界可以藉此製出間距遠小於20奈米的導線/間隔圖形,進而避免仰賴High-NA EUV多重圖形化製程。

未來能不能實現這項技術將取決於產業需求及面對技術發展障礙的能力。舉例來說,imec正在透過模擬來研究運用Hyper-NA EUV進行成像的可行性。其中一項議題是進一步縮短焦點深度(DOF,簡稱為焦深),DOF會隨著數值孔徑平方的反比而縮小。目前的可用總焦深對業界來說依然適用於生產嗎?另外,可以怎麼處理這些有限的焦深資源? 然而,如同前幾代的光學微影技術,最終決定還是會由成本的降幅來主導。重點在於找到經濟意義上的甜蜜點,也就是當引進新技術的成本與益處開始超越與舊技術相關的更多挑戰的那個時間點。」

減少二氧化碳當量足跡

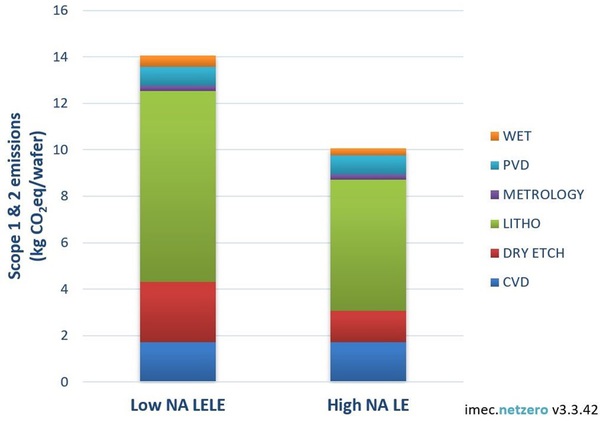

Steven Scheer表示:「我們運用了自家的虛擬晶圓廠模型imec.netzero來量化從low-NA多重圖形化轉移到High-NA EUV單次曝光的環境影響。二氧化碳排放的一個主要來源是微影時的電力消耗。我們的模型顯示,在單次曝光時,0.55NA曝光機EXE:5200所消耗的電力多過0.33NA曝光機NXE:380,這是在假設極紫外光源和晶圓產量相同的情況下。這主要是因為晶圓平台及光罩平台的速度必須加快,才能在High NA EUV的曝光長度更短的情況下維持產量。曝光之所以受限是源於更高數值孔徑所用的變形鏡片。

儘管高數值孔徑曝光機的功耗更高,但我們的模型顯示,把一次low-NA EUV雙微影蝕刻(LELE)製程模組改為High-NA EUV單次曝光能降低30%二氧化碳總排放量。簡化製程的影響勝過加速製程平台相關的功耗增加。透過最大程度提高曝光機的產量就能控制功耗,產量即機台每小時產出的晶圓數量(wph)。減少光阻劑量並管理晶粒大小/光罩佈局都是維持最大產量的關鍵,因為這兩者影響著High-NA EUV曝光機完成晶圓曝光所需的時間。

| 圖二 : 本圖顯示以High-NA單次曝光取代low-NA雙微影蝕刻(LELE)能減少30%二氧化碳排放當量。這兩種案例皆假設額定產量為220wph。 |

|

除了微影之外,蝕刻製程對於二氧化碳直接排放的影響甚鉅。多數的乾式蝕刻需要仰賴氟化物,這些物質的全球暖化潛勢(global warming potential)遠遠高於二氧化碳。我們開發製程與設計指南,以減少這些氟化物的排放。

| 圖三 : imec運算技術及系統/運算系統微縮研究計畫的資深副總裁(SVP)Steven Scheer |

|

除了排放量還有其他考量,例如材料匱乏與使用像是全氟與多氟烷基物質(PFAS)等有毒物質。PFAS是半導體製造多個面向的內部推手,包含化學放大阻劑(CAR)與清洗材料。High-NA EUV可能會首次引進金屬氧化物阻劑(MOR)這種不含PFAS的阻劑。我們近期展示了利用MOR薄膜阻劑製作小型導線/間隔圖形所取得的優良性能,以及運用MOR阻劑和二元式明場光罩來生產接觸孔洞圖形的優異表現。

然而,化學放大阻劑未來仍會是處理重要性較低的元件特徵圖形化的可靠技術。我們已經夥同我們的供應商社群,發起了全新的研究倡議來探索無PFAS或減用PFAS的替代選擇並衡量這些替代材料的性能。」

(本文由imec提供;編譯/吳雅婷)