在十年之前,談2奈米(nm)製程晶片的量產,那簡直就像天方夜譚,幾乎是難以想像的生產技術。但如今,台積電已經正式宣布了量產時程,這個原本市場以為不可能的晶片製程技術,將會在2025年正式量產。

而台積2nm技術的宣布有什麼重要性?它又會帶出哪些半導體製造技術的風向球?本文就從技術演進,以及競爭與成本的角度來切入分析。

FinFET微縮之路劃上休止符

台積電的2nm技術的宣布,單就技術上來說,就是正式宣告「鰭式場效電晶體(FinFET)」的微縮之路的終結。這個堪稱是近十年以來,台積電最具競爭力的晶片製程技術,最終都須止步於3nm。

毫無疑問,FinFET是個好東西,它除了讓摩爾定律得以延續外,同時也讓晶圓製造廠可以持續提升晶片的效能並縮小體積。它最大的特色就是採用了立體式的結構,改善了MOSFET的電路控制性能,並減少漏電流的發生,另一方面也縮短了電晶體的閘長。

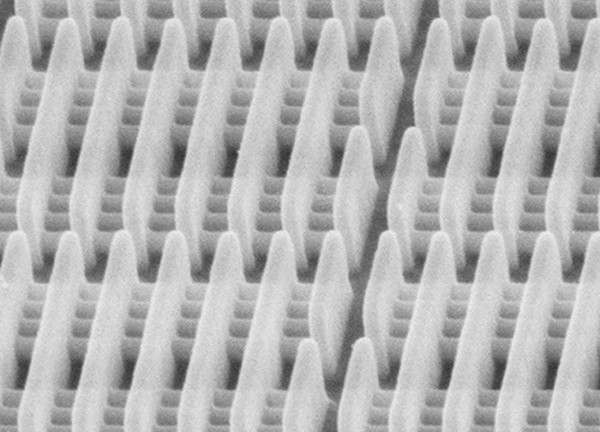

| 圖一 : 台積在2013年11月宣布成功試產FinFET,採用16nm生產製程。(source:TSMC) |

|

台積是在2013年11月宣布成功試產FinFET,而當時所採用的生產製程是16nm;英特爾則是更早於台積,是在2011年就已經推出了商業化的22奈米FinFET製程技術。

至於三星,則是在14nm製程才採用了FinFET架構,不過當時他們是處於追趕的位置,還因此跳過了20nm製程,直接進攻一個全新世代的技術,並且取得了相當的成果,可以說是一次成功的策略。

但走到現在,也就是4nm和3nm這個關口,FinFET的微縮之路終究來到了盡頭。由於單片的鰭式電晶體結構在這個製程之下,其電子控制的效能會大幅度的衰減,變得十分不穩定,因此難以作為先進運算的核心技術,自然也無法延續摩爾定律對性能提升的要求,於是採用新架構的呼聲就不斷在產業界與學研界裡響起。

雖然FinFET製程到了5nm以下就變成了一個關卡,但台積依然透過他們強大的晶片製造能力,硬是讓FinFET走到了3nm。而三星則是選擇在此節點轉向次世代製程。這除了顯示台積超越業界的製造能力外,更凸顯了台積對於獲利與成本控制的高度重視。

三星搶推GAAFET製程 企圖彎道超車

洞悉到FinFET的極限之後,晶圓製造業者們當然就開始著手進行相關的研究布局,以因應未來的先進製程服務之爭。但說白了,現在市場上也就只剩下三星和台積兩家公司有能力進行實際的量產,所以目前若要尋求3nm以下的晶片製造服務,就是一個非T及S的局。誰先端出,誰就贏了,至少表面上是這樣子。

也由於現在這兩強之爭的局面,讓落後的三星不得不採行較為激烈的「彎道超車」策略,企圖在3nm這個製程世代上,就開始導入新的電晶體架構技術,並期望藉此追上,甚至是超越台積電。

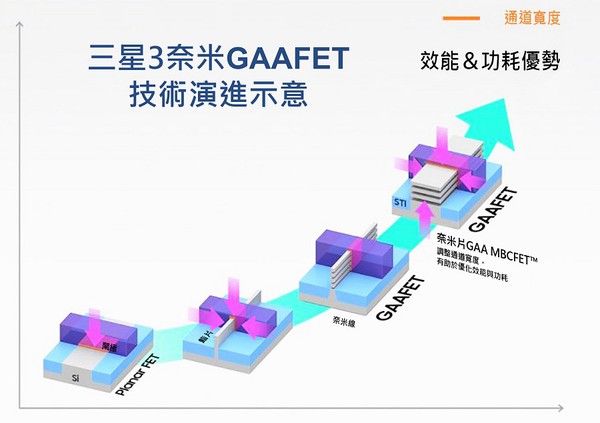

而三星他們選擇的製程稱為GAAFET「Gate-All-around Field-Effect Transistor」。

依據三星的說明,它們的GAAFET是一種採用自行研發通道較寬的奈米片結構,也就是自有的「MBCFET(Multi-Bridge Channel FET)」技術。相較於較窄的奈米線GAA技術架構,這種寬型的結構可以帶來更高的效能與更佳的能源效率。

| 圖二 : 三星GAAFET製程技術的示意圖。(source:三星) |

|

此外,三星也指出,相較於5nm製程,他們第一代3nm製程能降低45%功耗、提升23%效能、縮減16%面積;第二代3nm製程則可降低50%功耗、提升30%效能,並縮減35%面積,可全面優化晶片PPA指標。

但三星這個技術的宣布,最重要的還是宣傳的目的,因為三星所有的盤算就是要搶先台積之前,讓市場知道,他們的GAAFET已經開始正式量產,而且是全球第一家的3nm晶片製造商。

不過其實是不是3nm並不這麼重要,最值得關心的,是三星開始導入了新的電晶體製程技術。但到目前為止,他們良率與客戶都屬於未知的狀態,成本與獲利更是仍待觀察。

台積以王者之姿 穩穩跨進奈米片世代

儘管三星沒有特別強調,但我們從其所提供技術示意圖來看,就可以得知他們的GAAFET技術就是一種奈米片(Nanosheet)架構,而這跟台積所發表的 N2技術,其實都是屬於同一種技術類型。換句話說,未來市場上2nm以下的製程晶片,都會是使用奈米片架構的電晶體。

相較於三星採用大動作追擊的策略,台積對於導入奈米片架構製程就顯得保守且小心,或者說是一種不疾不徐的態度。我們回顧台積選擇進入FinFET製程的時間點來看,就可以端倪出這家公司的決策文化。

一來,他們已是市場的領先者,穩健拓展業務遠比大膽推進技術更為重要;再者,台積一向看重生產良率和高獲利率,不穩定、不夠成熟的製程,他們定不敢,也不會貿然進行量產。

就因為這立場與策略的差異,因此台積選擇進入奈米片架構的時間點,也就晚了三星一個世代。而這個一世代的差異,除了讓台積在3nm製程上有更好的成本優勢外,也為他們的2nm製程取得了更多的研發和試產的時間。

依據台積自己公布的資料,相對於N3,新一代的N2技術在相同功耗下,速度提升了10~15%;在相同速度下,則功耗降低25~30%。而在應用領域方面,N2將會推出針對行動運算的基本版本,另也會推出高效能版本和小晶片整合的解決方案,預計在2025年開始量產。

不過這裡就有一點性能上的差異,因為三星的3nm GAAFET是對比5nm FineFET,而台積N2則是對比N3,所以單就各自帳面上的性能提升來看,奈米片架構的的確確是能夠突破FinFET的極限。若是比較雙方的數據差異,則台積擁有微縮製程上優勢,其2nm具有較好的功耗表現。

不過三星的2nm製程也預計在2025量產,目前其實際的效能數據則仍未公布。

奈米片成為產業共識 但誰會需要2nm技術?

對於台積與三星皆選擇了奈米片架構作為下一代的製程技術,其實一點都不令人意外,甚至可以說是一種必然的結果。比利時微電子研究中心(imec)就曾在一篇技術文章中指出(註1),奈米片可以視為FinFET的自然演變,它能讓許多針對FinFET製程應化的模組,都能沿用至奈米片製程。也促使業界更容易接受這套新架構。

不過,FinFET與奈米片畢竟不相同,在製程上仍有不小的差異。Imec也指出了它們的四大關鍵差異,且需要特別研發創新技術。

首先,奈米片會利用矽(Si)與矽鍺(SiGe)進行多層的磊晶成長,致使傳統的CMOS製程不再適用。而且整個堆疊會進行圖形化,製成高深寬比的鰭片,因此確保奈米片的型態是個挑戰。

第二個差異,是需要導入一層內襯層,也就是增加一層介電層來隔離閘極與源/汲極,進而降低電容。

第三個差異是奈米片製程多了一個釋出通道的步驟,而此過程需要高度選擇性,才能把少量的鍺留在奈米片之間,並降低矽材的表面粗糙度。

第四個差異是替代金屬閘極的整合,包含在奈米片周圍與彼此間的間隙內沉積金屬,並進行圖形化。

而從imec所指出的製程挑戰可以看出,進入奈米片結構製程的困難其實不小,直接造成的就是製造成本將大增,同時短時間內的良率應該不會太高,真要下單投入生產,所要承擔的商業風險其實不小。尤其是目前3nm製程的生產成本已經將近6億美元,若再往下走到奈米片的2nm,則金額實在難以想像。

所以綜合來看,屆時能有足夠資本實力可以下單2nm製程晶片的業者,其實已經屈指可數。目前看來如果不是蘋果(Apple),就是全力追求高性能與低高耗的繪圖與處理器業者,例如NVIDIA和AMD,其他的行動運算平台業者如高通或聯發科等,現在都還難以推估他們屆時是否具備足夠的商業能力來投單。

當然,Google和Amazon,或者特斯拉,也有可能投單2nm晶片,因為他們的資本更加龐大,同時所需要的效能表現又更加刁鑽。

至於中國的業者也不應該被排除在外,畢竟2025年還有一段時日,美中的衝突也存在解除的可能性。

結語

整體來說,半導體微縮製程再往下走到2nm已是即將發生的事實,而摩爾定律也還能再繼續維持下去,人們也將繼續感受到電子裝置與科技應用不斷創新的便利性,尤其是在運算與AI處理的體驗上。唯一的問題,就是這超級龐大的製造成本究竟有多少人可以負擔。所以可以想見的是,再往下探的微縮製程可能不再具備多少意義,先進的半導體整合與異質設計,可能才是日後晶片開發者需要關注的所在。

刊頭圖(source:TSMC)

註[1] imec,評比奈米片、叉型片與CFET架構;CTIMES,2022年4月