先進晶片的設計與製造,已經是龐然大物,一般的人力早已無力負擔。幸好,AI來了。有了AI加入之後,它大幅提升了IC設計的效率,無論是前段的設計優化,或者是後段晶片驗證,它都帶來了無與倫比的改變。

這當然其來有自,但卻也沒有那麼理所當然。我們可以從一顆先進處理器晶片裡的電晶體數目看出一個端倪。

以蘋果最新一代的M2 Pro處理器為例,它具備了400億個電晶體,數量已遠遠超過人類的腦神經細胞(140億個)。如此多的電晶體數量,當中還牽涉了無數的電路布局和邏輯整合,想要單靠人力來開發,幾乎就是個不可能的任務,就算是阿湯哥親自上場,恐怕也無能為力。

再加上越來越緊迫的上市時程和越來越短的產品生命週期,一顆晶片從規格設計開始,到行為描述、RTL階段,再到邏輯設計和轉成電路的布局,接著驗證等等,若沒有點石成金的工具,即使是擁有最新鮮的肝,晶片工程師們也沒有辦法如期完成,只能束手就擒。

雪上加霜的是,IC設計的人才正持續面臨短缺。根據SEMI國際半導體產業協會的資料,至2030年之前,光是美國半導體設計產業就可能面臨高達23,000名的半導體工程師人才缺口,更遑論如今的半導體重鎮-亞洲地區。

痛點很痛,但卻AI姍姍來遲

所以,把重複性的工作交給電腦來做,將是最佳的解法。最好它能夠自己找出盲點來,把初步的設計進一步優化,甚至還可以跳過一些流程,讓自動化工具自己來生成,工程師們只需要站在創意的原點上來思考。而這就是目前IC設計的現在進行式。

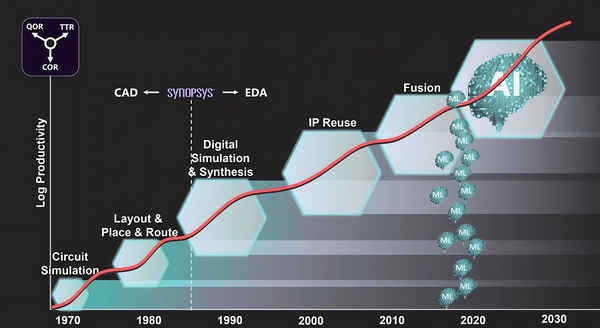

只不過晶片設計也不是一天就變得這麼複雜,工程師們更不是今天才需要AI自動化的協助,實在是10年之前人工智慧技術是個冷門學問,且在生產製造領域鮮少有導入的實例,直到Google AlphaGo的問世。

AlphaGo的貢獻不僅是證明了AI能讓人類「棋逢敵手」,最大的影響還是它開啟了AI的應用市場,也讓束之高閣的深度學習和神經網路技術找到了普及的路徑。大家這時才赫然發現,原來從數據裏頭撈出的東西可以這麼有影響力。

只不過光有AI軟體演算法還不夠,仍需要相對應的硬體搭配才能實現最佳的性能,於是GPU和神經網路加速器種種相關的元件商也陸續加入,最終開啟了目前的大AI時代。而一直等待神隊友出現的IC設計師們,也終於在這段時期看到了AI輔助設計的應用潛力。

| 圖一 : AlphaGo最大的影響還是它開啟了AI的應用市場。(source: Google) |

|

DeepMind啟發 新思科技推出首款商用EDA AI方案

首款針對IC設計的商用EDA方案,是新思科技(synopsys)在2020年初所發表的「DSO.ai」工具。根據新思的說法,會推出DSO.ai解決方案,就是受到DeepMind所開發的AlphaGo與AlphaZero的啟發,希望能夠過AI技術在極大量的晶片設計方案中自主搜尋優化目標。

新思科技DSO.ai工具的厲害之處,就在於它可以大規模探索晶片設計工作流程中的可能選項,同時自動執行後續決策,大幅提升晶片設計團隊的工作處理量。而運用在實際的晶片開發中工作,它僅需耗費少量的時間和較少的資源就能達成目標。

在EDA領域初試啼聲就一鳴驚人之後,新思科技當然也就打鐵趁熱,持續精進他們的AI輔助技術。近期新推出的「Synopsys.ai」即是他們集大成之作,幾乎是把AI技術全面應用在晶片設計流程之中,目的就是要讓晶片開發可以更加完善。

依據新思的資料,Synopsys.ai是業界首款全面涵蓋設計、驗證、測試和製造等流程的AI驅動EDA解決方案,而且可用在數位和類比晶片的設計上。其最大的特色就是讓工程師能在晶片設計的每個階段,包含系統架構到設計和製造等階段,都可以使用AI技術,並且透過雲端來存取這個解決方案。

新思表示,Synopsys.ai EDA套件包括了數位設計空間優化,可實現優化功耗、效能和面積(PPA)目標;至於類比設計自動化,是用於各式製程節點的類比設計快速遷移(migration);以及驗證覆蓋率收斂(coverage closure)和迴歸 (regression)分析,以實現更快的功能測試收斂、更高的覆蓋率和預測性錯誤檢測。

另外,Synopsys.ai也具備自動生成測試的功能,可以減少並優化矽晶缺陷覆蓋率的測試圖型(pattern),並實現更快速的結果效率(time to result)。再加上生成可加速高精度曝光(lithography)模型開發的解決方案,能帶來最高良率。

新思指出,達成驗證覆蓋率目標是晶片設計中最耗時的步驟之一,因為需要進行收斂與迴歸分析,這需要掌握廣泛的測試覆蓋範圍。Synopsys.ai可在跨製程節點快速遷移模擬設計上實現自動化流程,生成測試案例。並根據事先定義的測試覆蓋目標和限制,利用歷史數據生成新的測試案例,如此可增加覆蓋範圍並確保更精準的預測性錯誤檢測,減少手動生成測試的需求。

此外,自動測試生成功能可減少矽缺陷的覆蓋範圍,並優化測試模式,加快獲得結果的時間。而機器學習可以透過訓練識別晶片設計中潛在故障的模式和指標,根據歷史數據進行學習,使得晶片設計人員能夠更快、更準確地檢測和診斷故障,降低驗證過程中出現錯誤和延遲的風險。

而根據新思客戶的回報,在減少功能覆蓋漏洞方面,AI工具的效能提升了10 倍,且IP驗證效率也提高30%。

| 圖二 : 從現在開始,EDA工具將進入AI驅動的年代。(source: Synopsys) |

|

朝向智慧系統設計 Cadence打造全方位的EDA AI平台

另一家EDA方案大廠,益華電腦(Cadence Design Systems, Inc.)同樣也看到了AI所能帶來益處,並陸續在EDA方案中加入AI輔助的功能。不同於其他的EDA業者,Cadence並不打算只把AI的技術侷限在晶片設計領域,而是更強調從系統的觀點來出發,也就是要從晶片設計開始,一路跨到系統設計上,都能有AI的助力。

針對智慧系統設計(Intelligent System Design)中的AI功能與角色,Cadence資深副總裁暨數位與簽核事業群總經理滕晉慶(Chin-Chi Teng)博士表示,AI能讓晶片業者更具生產力,透過AI技術,將可以取得更佳的PPA(功耗、性能與面積)效能、更好的驗證收斂、以及更快的設計週期。

以Cadence的AI驗證平台Verisium為例,它能夠確定錯誤的優先順序、追蹤錯誤、發現其根源,然後修正問題。而這個工具是基於Cadence的整合型企業數據和AI(Joint Enterprise Data and AI,簡稱JedAI)大數據平台,並與Cadence 驗證引擎自然整合。

透過Verisium,所有驗證數據,包括波形、覆蓋範圍、驗證報告和文件,都可匯集於JedAI平台。並利用機器學習(ML)模型,從所收集的大數據中挖掘其他專有指標、啟用新的工具,從而提高驗證效率。

另一個案例是數位化全流程。滕晉慶(Chin-Chi Teng)指出,Cadence的Cerebrus智慧化數位晶片設計工具,是一款以機器學習為技術基礎所開發的新型工具,它可實現數位晶片設計自動化和規模化,不只能以更快速度產出結果,還能產出更好的結果。相對於傳統的設計方式耗時數月的時間,若採用Cerebrus工具,則一位工程師只要10天就能取得20%的PPA提升。

滕晉慶解釋,Cerebrus的AI技術具備獨特的強化學習引擎,可自動優化軟體工具和晶片設計選項,提供更好的PPA,進而大幅減少工程端的負荷和整體流片時間。例如,Cadence Cerebrus 布局優化功能,進一步縮小晶片尺寸。

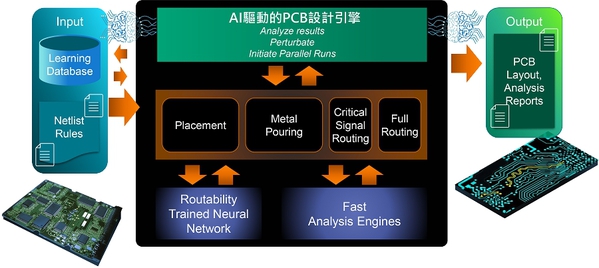

近期推出的Allegro X設計平台,更是業界首款針對系統設計的工程平台,它以Cadence Allegro與OrCAD核心技術,可整合電路圖、佈局、分析、設計協作與資料管理。 而其AI技術,在設計效能和自動化方面更展現革命性的提升。

根據Cadence資料,其全新的AI技術在PCB設計領域上達成了出色的成果,與手動進行的電路板設計相較下,大幅縮減了PCB設計的時間。能把PCB佈局和繞線的任務從幾天縮短到數分鐘,同時帶來同等或更高的設計成果。

| 圖三 : 透過Cadence的AI設計平台,PCB的設計時間將可以大幅的縮減。(source:Cadence) |

|

減輕工程師設計負擔

隨著AI的出現,除了為IC設計流程帶來了更大的優化潛力,並對EDA設計工具產生了深遠的影響。AI技術應用在IC設計的各個階段都非常適宜,從前段的電路結構和元件選擇,到後段的物理佈局和佈線優化。AI演算可以透過優化搜索、自動化生成和快速評估設計方案,幫助設計師在設計空間中快速找到最佳解決方案,大幅提升設計效率。

AI技術在IC設計的後段驗證和仿真階段也發揮著重要作用。傳統的驗證和仿真過程往往耗時費力,尤其對於大型複雜的IC設計來說。AI技術可以運用在快速建模和預測、錯誤檢測和修復等方面,加速驗證流程,幫助設計師更早地發現和解決問題,減少驗證時間和成本。

針對物理佈局和佈線的階段,AI能夠實現更高程度的自動化。AI演算法可以根據特定的設計規則和性能目標,自動生成佈局和佈線方案,並在不同設計的限制下進行快速優化。這不僅減輕了設計師的工作負擔,還有助於改善晶片的性能和功耗。

另外對於電源和散熱管理,AI技術也可以做到更有效的解決。在IC設計中,電源和散熱是關鍵問題,直接影響設計的可靠性和性能。AI可以直接對晶片進行數據監測和分析,自動調整電源供應和散熱系統,實現更有效的功耗管理和熱管理策略。至於在故障檢測和容錯設計方面,AI可以幫助設計師更早地發現潛在的故障點,並提供更優化的容錯機制,使IC設計更加穩健和可靠。

結語

AI為IC設計流程帶來了更多的智能化、自動化和高效化。不僅加速了設計過程,降低成本,同時還能幫助設計師在設計空間中探索更多可能性,提高設計的品質和性能。至於AI技術的導入可能帶來新的挑戰和問題,例如安全性和隱私等問題,也需要在應用中加以考慮並解決。