對台灣而言,八月份仍然是相當炎熱,卻也是台灣半導體產業開始邁入熱鬧的時間點,一般來說,通常都是由EDA(電子設計自動化)暨IP(矽智財)供應大廠Cadence(益華電腦)先打前鋒,為全球半導體產業發展趨勢的交流互動,揭開熱鬧的序幕。

各方菁英 齊聚CDNLIVE 2015

CDNLIVE對Cadence乃至於全球半導體產業一直都是重要的年度技術論壇,隨著產業所面臨的挑戰日益嚴峻,從EDA、IP、晶圓代工與IC設計等業者在實務上所面臨的問題,自然也就不容小覷,而CDNLIVE的內容除了探討未來的發展趨勢外,針對諸多重要技術議題,亦有相當深入的討論。CDNLIVE 2015今年參加的人數超過700餘位,相較於歷年人數,又再度創下歷史新高。而今年大會主題演講的講師陣容,除了Cadence資深副總裁暨策略長徐季平博士之外,亦有台積電設計暨技術平台副總經理侯永清博士、清華大學副校長吳誠文博士、聯發科設計技術研發本部總經理黃世安博士以及亞馬遜雲端運算服務(Amazon Web Services)資深業務開發主管David Pellerin等人。

| 圖1 : CDNLIVE 2015的主題演講講師暨Cadence高階主管群 |

|

先進製程帶動市場機會 也帶來設計挑戰

近年來,Cadence打算從單純的EDA供應商,轉型成為EDA/IP暨系統層級方案的供應業者,與此同時,Cadence在半導體上游仍然有相當比例的耕耘。延續了既有的基調,徐季平以啟動系統設計創新為題,為現場學員分享未來科技產業的發展趨勢。他引述IBS Foundry Market Trends在2014年12月的預測數據表示,全球晶圓代工業者的主要營收將有相當大的比例來自先進製程,這包含了20/22奈米、14/16奈米以及未來將會發生的10奈米製程,預計到2020年,這些製程所帶來的營收就接近400億美金(總營收約為780億美金左右)。

| 圖2 : Cadence資深副總裁暨策略長徐季平博士 |

|

既然晶圓代工的營收有很大的比重來自先進製程,對於IC設計業者自然也會產生連動關係,根據IBS的統計,對於IC設計業者來說,設計與良率提升成本的增加,是現階段最大的挑戰,若將7奈米與28奈米相較,前者的成本明顯提升數倍之多,若進一步來看成本結構,軟體與驗證在先進製程所花費的成本更是驚人。

徐季平進一步指出,先進製程進入20奈米後,需要動用雙重曝光技術,這對於EDA供應商而言,必須將整體設計流程與相關工具再重新調整,以有效因應先進製程的根本性變化。所以在此次的主題演講中,徐季平以RTL到GDS生成的設計流程作為主體,向市場宣示了Cadence旗下各大工具與設計流程整合的企圖心,整個設計流程包含了Cadence旗下許多重要工具,像是Genus Synthesis、Innovus Implementation System、Tempus Timing Signoff、Joules RTL Power Solution、Quantus QRC Extraction、Voltus Power Integrity以及實體驗證系統等重要產品線。

所以從設計流程的第一步到最後一步,如果到最後出了問題,要重新再跑一次設計流程,時間上一定來不及,因此在思考設計流程與工具開發上,從設計流程的第一步開始到最後一步,都要同時考慮進去才行。他也談到,將設計流程所需要的設計工具加以整合的想法,Cadence早在七年前就已經著手進行,而這項重大工程約莫還需要兩年的時間才能大功告成,不過,截至目前為止,絕大部份的設計工具相較於過去都有效能上的明顯提升,換言之也達到了各自的里程碑。

從系統整合到晶片開發 解決方案完整度才是關鍵

除了設計工具的整合之外,Cadence近期也十分重視系統業者的發展動態,掌管亞太區的Cadence全球副總裁石豐瑜指出,過去在產業界,有許多人認為EDA在半導體產業的重要性日漸低落,但如果考量到晶片、軟體與系統層面之間的連動關係,其實就會發現,EDA業者能夠作的事情其實比他們所想像的還要多很多。

石豐瑜觀察,歐美與亞太地區市場的市場特性各有不同,歐美客戶群偏重取得EDA工具來實現產品層次的想法與創意,但亞太地區近年來出現許多新創或是系統層級的客戶,則是會從系統層面思考,在面對不同終端應用在實際環境所面臨的挑戰,關心的就是如何解決系統開發時所出現的問題,慶幸的是,Cadence的解決方案相當完整,能因應客戶需求來提供對應的工具。此外,系統整合業者若要開發自有晶片,可能沒有豐富的晶片設計經驗與基礎,Cadence甚至也要扮演顧問角色,協助建置晶片設計流程,沒有太多的犯錯空間,所以相較於過去,Cadence在市場上所面對的問題變得更為多元。

徐季平也補充說明談到,系統業者其實才是最能實現創意的公司,從過去到現在,全球一線的系統整合業者都想要開發專用晶片以讓自己的產品性能達到最佳化,他也坦言,過去的確會有系統業者採購ASSP或是ASIC來完成系統設計,但下一個問題是,後續的營運維護要如何因應?再加上自行開發晶片會有不少的成本支出,這也是部份系統業者仍未採取行動的原因。

產業論文競賽 亦有豐碩成果

CDNLIVE大會的主要目的是提供Cadence使用者一個交流、互動、啟發創新的平台,因此已CDNLIVE連續三年舉辦了產業論文徵選,而在今年,論文評選委員會共由12位來自IC設計、ASIC與系統客戶的高階主管組成,包括聯發科、瑞昱、英業達與聯想等系統廠,其中論文主委由聯發科毛政智處長擔任。今年的委員會以創新、實用與完整性為標準進行論文評選,選出了三篇得獎作品,分別為:

表1 產業論文競賽得獎作品

最佳論文 |

The Challenge and Experience Sharing on 16nm Chip Implementation

創意電子(李佳燕) |

優秀論文 |

Early Detection of Layout Induced Stress Effect in 28nm UMC Process Technology

聯華電子(羅志文) |

Power State Validation To DVFS Design by Using Pattern-less Verification

聯發科(林健偉) |

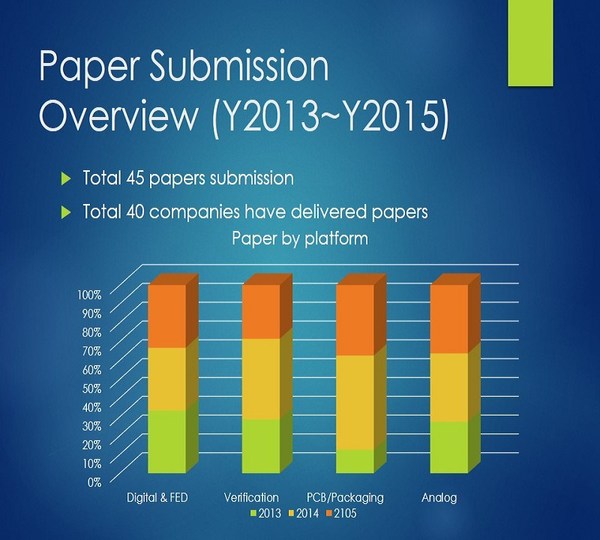

使用者論文徵選舉辦迄今,已經累積超過40家國內外企業的投稿。大致上,論文的種類可以分為:前端設計/數位實現、系統設計與驗證方案、印刷電路板/封裝以及類比等四大類別,每年的比重不一而足,這也顯見Cadence在不同領域皆有相當深入的著墨。

| 圖4 : CDNLIVE近三年的論文種類分布狀況一覽 |

|

結論

歷經近幾年的發展,Cadence儼然已經成為系統層級的方案供應商,在先進製程方面,除了在設計工具的整合展現強烈的企圖心外,與晶圓代工與處理器IP業者亦保持相當良好的合作默契,延伸至系統層級,今年也特別邀請到亞馬遜講師蒞臨CDNLIVE分享IoT產業趨勢,可見Cadence在產業界已經累積了可觀的基礎與成果,未來又將如何演變,值得期待。(圖片提供:Cadence)