除了晶片本身設計需展現優勢攻進人工智慧(AI)市場,搶占一席之地之外,PCIe高速訊號傳輸介面規範已成為支持實現人工智慧的關鍵應用技術,因此各家產品相當重視PCIe的應用效能。PCI-SIG是研發PCIe、建立一致性應用規範及提供正式合規認證的全球性組織,每年度都會到世界各國家推廣說明最新一代PCIe應用的相關資訊。

今(2024)年9月PCI-SIG DevCon開發者大會於韓國首爾舉行,此次主題介紹最新PCIe 6.0應用及測試規範,根據PCI-SIG協會發佈,當天現場參加者所屬的公司類別,結構已從往年廣為人知的幾家巨型企業轉變成數十家科技企業或AI新創公司,其中包括來自台灣的艾飛思科技(iPasslabs);而PCIe 6.0最終版應用規範預計2025年Q3發布正式推出合規規範。

| 圖一 : PCI-SIG DevCon Korea 2024現場照片(source:艾飛思科技) |

|

在經過實際走訪數家AI晶片新創公司以後,真實感受到韓國的相關產業正在積極發展並迅速成長,許多從全世界大型科技企業出來的人才自立門戶創立公司,這些公司各自發展不同的AI相關技術產品,包括神經處理器(Neural network Processing Unit;NPU)及資料處理器(Data Processing Unit;DPU)等,應用範圍從資料中心到邊緣計算,皆強調高效能、低功耗且低成本,各家期望能在全世界AI市場占有一席之地為目標。茲舉例說明如下:

FuriosaAI

FuriosaAI由來自三星、高通、AMD的工程師於2017年創立,在今年八月的 Hot Chips大會上,發表第二代AI加速卡「RNGD」,預計將於2025年初廣泛上市。

RNGD致力於成為資料中心最有效率的大型語言模型(LLM)和多模型推理加速器,在以傳統晶片製造商所主導的市場上,RNGD 因其高性能、可編程性和低功耗的優勢而備受關注,RNGD的初期測試顯示,在大型語言模型(如GPT-J和Llama 3.1)上取得了令人鼓舞的成果。

單張RNGD PCIe 5.0卡對於約100億參數的模型目標能夠提供每秒2,000到3,000個token的吞吐量,值得關注的耗電部分,TDP僅150W,相比之下著名的GPU則超過1000W的功耗。並結合先進技術,包括48GB的HBM3記憶體、創新的張量收縮處理器(Tensor Contraction Processor),以及完整軟體堆疊搭配通用編譯器。

今年5月FuriosaAI與艾飛思科技(iPasslabs)合作,艾飛思科技為首版晶片提供「PCIe 5.0 合規前期性測試」服務。RNGD既順利於7月通過認證,被列入官方 PCI-SIG合規產品名單,首版晶片樣品僅三個月便「一次通過」,這顯著表現將使RNGD未來能成為數據中心和大型語言模型推理的最佳應用解決方案。

| 圖二 : FuriosaAI’s AI加速卡RNGD,下方一排即是PCIe。(source:艾飛思科技) |

|

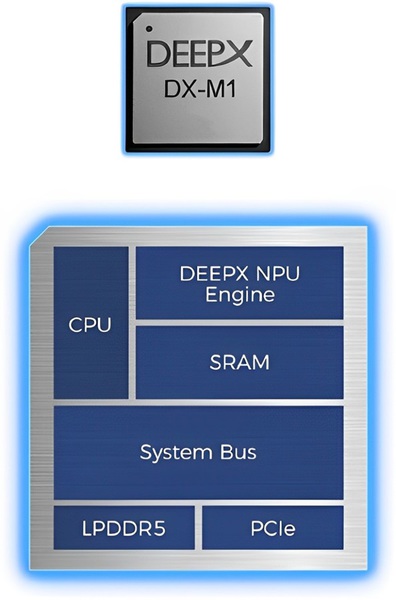

DEEPX

DEEPX是筆者此次實際拜訪韓國AI晶片新創公司之一,印象頗深刻,DEEPX是邊緣人工智慧晶片新創公司,NPU模仿人腦運作,具有低耗能和降低生產成本的優點,DEEPX為不同電子設備的AI應用設計硬體及軟體模組產品,推出包含4款晶片組成的All-in-4 AI 全面解決方案,因為多項專利技術革新還獲得2024 CES展3項創新?。

舉例來說,DX-M1是DEEPX的旗艦AI晶片,DX-M1精心設計以便無縫整合至各種AIoT應用中,可同時支援處理多達16個多頻道視頻,並能以每秒超過 30幀(FPS)的速度進行即時AI計算處理,PCIe通道,DX-M1封裝在M.2模組中,使任何人都能輕鬆在開放硬體平台上運行AI。

| 圖三 : DEEPX DX-M1 晶片架構圖(source:艾飛思科技) |

|

PCIe已成為最主要且普遍的I/O介面,運算晶片與各種周邊裝置以及其他I/O介面透過PCIe相互連結,作為高速資料傳輸功能。

由於生成式AI近兩年潮流興起,為了因應AI晶片計算出的資料能夠大量且高速傳輸到其他應用平台,並且要求低延遲、低功耗,PCI-SIG持續積極研發更新一代,才能讓高效能AI晶片實際應用在現實生活中。目前大部分AI晶片相關產品高速訊號傳輸介面使用到PCIe 5.0,PCIe 6.0 正式可認證的測試規範則預計於2025年Q3釋出。

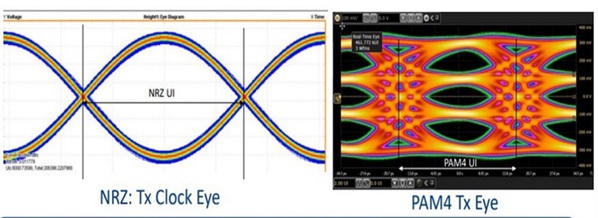

PCIe 6.0傳輸速度加倍,從PCIe 5.0的32GT/s至64GT/s,PCIe 6.0為了提升傳輸速度選擇採用PAM4(Pulse Amplitude Modulation 4-levels)編碼,透過前向錯誤更正(Forward Error Correct)和循環冗餘檢查(Cyclic Redundancy Check)減少PAM4訊號傳輸相關的位元錯誤率,Flit(流量控制單元)基於編碼支持PAM4調變,並且與FEC和CRC共同執行,以實現雙倍頻寬。

| 圖四 : PAM4眼圖(source:艾飛思科技) |

|

相較之下,PCIe 6.0 Compliance test(合規驗證)比對之前的5.0驗證規範多了兩項測試:RLM(Ratio of level mismatch)以及SNDR(Signal-to-noise and distortion ratio)。

RLM是衡量訊號不同電平之間不匹配程度的指標,不同電平之間的距離應該是一致的,以確保訊號準確性;由於硬體設計或訊號傳輸過程中的不理想情況,可能會出現不匹配現象,RLM幫助檢測電平之間不匹配的程度,以確保訊號的可靠性。SNDR表示訊號與噪聲和失真之間的比值,包括所有的噪聲和失真成分。SNDR數值越高,表示訊號質量越好,噪聲和失真相對成分越少。

結語

隨著全世界科技迅速發展,不僅是近兩年掀起熱潮的生成式AI,亦或是元宇宙、雲端伺服器及無人車等,巨量資料傳輸、高效能、低延遲,以及日益關鍵的低耗能,各種科技產品需具備這些特性,因此產品設計結構益趨複雜,尤其I/O介面訊號傳輸應用技術,在研發階段變得越來越困難。

然而,如今科技產業鏈已為百家爭鳴、兵家必爭之地,技術更迭速度加快,產品更需競爭優勢,時間、金錢、成本皆高效率,更是成為各家科技公司追求的關鍵。

台灣艾飛思科技執行長沈忠榮表示,由於他在訊號量測業界已從事20餘年的豐富經驗,因此對於科技界的演化感受深刻,尤其是PCIe及High-Speed Ethernet I/O介面,因應AI以及智能車輛,無人機等科技的相關應用需求,每新一代推出到市場的時間間隔以驚人速度從原來6到7年縮短成2至3年的時間。

台灣艾飛思科技致力於高速訊號技術的最新開發,並且是PCI-SIG的工作小組成員之一,不僅參與研發技術會議,每兩個月就會參與PCI-SIG Compliance Test Workshop 合規驗證測試項目。

從設計階段的SI/PI模擬分析、晶片實際開發後的驗證除錯,可稱為「合規前期性測試」(Pre Compliance Test),至最後官方PCIe認證階段,艾飛思科技團隊能在Workshop現場成為最前線救援,協助顧客順利拿到認證,節省時間金錢成本,就如同團隊協助韓國FuriosaAI客戶,僅花兩至三個月的時間即得到PCIe 5.0一致性合規認證。2025年後將有更多AI產品應用PCIe 6.0作為資料傳輸通道,台灣艾飛思科技將為產業顧客提供最佳化解決方案。