本文介紹相位陣列混合波束成形架構中接收器動態範圍指標的測量與分析的比較。測量使用32通道開發平台進行驗證分析。本文上篇回顧子陣列波束成形接收器的分析,重點是處理類比子陣列中訊號合併點處的訊號增益與雜訊增益之間的差異;下篇則分析開發平台接收器性能,並與測量結果進行比較。最後,就觀察結果討論,藉以提供一個可用於預測更大系統性能的測量與建模基準。

相位陣列波束成形架構大致可分為類比波束成形系統、數位波束成形系統或以上兩者的某種組合—採用類比子陣列,經過數位文書處理後形成最終天線波束方向圖。後一類(基於數位組合的子陣列)結合類比和數位波束成形,通常稱為混合波束成形。

在業界對軟體定義天線的探索中,人們希望實現全數位相位陣列,以便大幅提高天線方向圖的可編程性。在實踐中,特別是隨著頻率提高,封裝、功耗和數位處理方面的挑戰迫使人們減少數位通道數。混合波束成形緩解了建置工程師常常面對的數位通道密度需求,因此可能會在未來某個時間作為一種實用方案出現。

圖1展示一個代表性混合波束成形架構,顯示該架構中包含的主要子系統。大多數混合波束成形系統都是此一概念的某種變體。從右到左觀察框圖,可以直覺理解該架構:空中的波前入射到天線元件,經過微波電路到達資料轉換器,再進行數位文書處理後形成最終的數位波束資料。框圖將混合波束成形架構展示為七個子系統的組合:

1.天線元件:將空中的微波能量轉換為同軸介質上的微波訊號。

2.發射/接收(T/R)模組:包含接收低雜訊放大器(LNA)和發射高功率放大器(HPA),以及用於在發射和接收之間進行選擇的開關。

3.類比波束成形:將選定數量的元件組合成一個類比子陣列。

4.微波上/下變頻:如果工作頻率大於資料轉換器的工作範圍,則使用頻率轉換將工作頻率轉換為適合資料轉換器處理的中頻(IF)。

5.資料轉換器:將微波頻率轉換為數位。

6.數位上/下變頻:隨著高速資料轉換器的普及,資料轉換器的速率通常大於處理頻寬所需的速率。使用資料轉換器積體電路(IC)中嵌入的數位上/下變頻特性,將同相/正交相位(I/Q)資料流程降低到與應用的處理頻寬相稱的較低速率,可以節省系統功耗。

7.數位波束成形:最後,將I/Q資料流程加權合併,形成最終的數位波束資料。

微波工程師在混合波束成形架構中面臨的挑戰之一,是隨著系統架構的演變進行性能預測。串聯微波分析相關文獻非常完備,數位波束成形測量也有文獻記載,但實測與建模得到的混合波束成形微波指標比較方面的文獻還很有限,缺乏一個用於外推到更大系統設計的基準。

本文將討論混合波束成形系統的接收器動態範圍分析,並比較一個32元件混合波束成形測試平台的測量值和預測值。最初開發的混合波束成形原型平台是為了在一個代表性架構中驗證IC設計,並支援X波段(8 GHz至12 GHz)相位陣列架構的快速原型設計。

然而,隨著表徵的開始,很明顯需要一種系統性預測性能指標的方法。我們的目的是記述分析方法以及測量資料的比較,使工程師能夠利用一個經表徵的基準來建構類似但更大的系統。

原型硬體

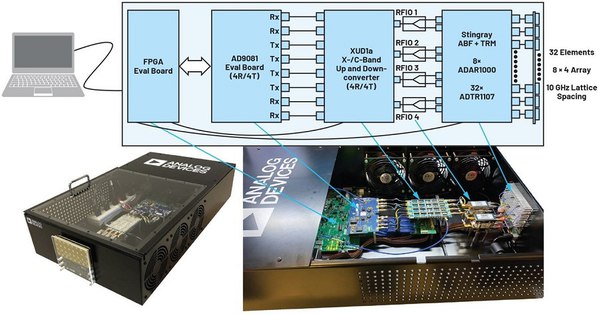

我們開發了一個32元件的混合波束成形原型平台,如圖2所示。詳細訊號鏈如圖3所示。

| 圖2 : X波段(8 GHz至12 GHz)相位陣列原型設計和開發系統 |

|

前端由32個發射/接收模組和8個類比波束成形IC(BFIC)組成。兩個BFIC輸出組合產生四個8元件子陣列。四個子陣列連接到一個4通道微波上/下變頻器。該4通道微波上/下變頻器再連接到一個包含四個類比數位轉換器(ADC)和四個數位類比轉換器(DAC)的數位轉換器IC。ADC以4 GSPS採樣,而DAC以12 GSPS採樣。

微波頻率設定為8 GHz至12 GHz。內部本振(LO)設定為具有固定IF(中心頻率為4.5 GHz)的高端LO。在該IF頻率時,ADC在第三奈奎斯特區進行採樣。

利用一個商用FPGA板進行資料擷取,我們開發一個MATLAB電腦控制介面,以便能夠在真實硬體中快速表徵模擬波形。資料分析及後續處理在MATLAB中進行。

類比子陣列串聯分析

除訊號合併點外,所有傳統級聯方程均適用於類比子陣列的級聯分析。如果訊號在合併點處的幅度和相位匹配,並且雜訊不相關,那麼訊號增益和雜訊增益將不同。因此,需要一種方法來以不同方式追蹤這些項目。

所用方法

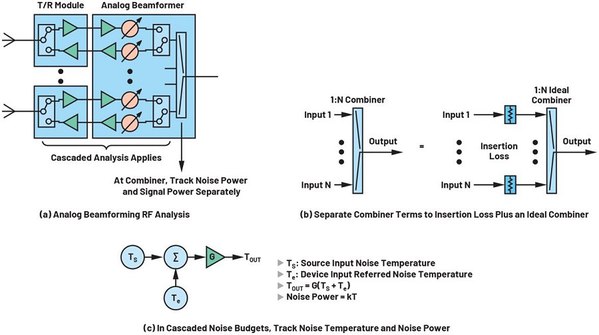

圖4說明了所使用的方法。圖4a顯示了訊號增益和雜訊增益分開的點。真正的合併器具有插入損耗項和理論合併項。這可以用圖4b來解釋。最後,如果追蹤雜訊溫度(如圖4c所示),那麼可以在每一級的輸入和輸出端追蹤雜訊功率。

| 圖4 : 一種用於模擬相關合併的串聯分析方法:分別追蹤訊號增益和雜訊增益。追蹤元件雜訊溫度和折合到輸入端的元件雜訊功率提供了一種分別追蹤這些增益項的方法。 |

|

為了計算任意級輸出端的雜訊功率,須將元件折合到輸入端的雜訊與輸入雜訊線性相加,然後轉換回dBm/Hz並加到元件雜訊增益上。

要根據元件雜訊係數計算折合到輸入端雜訊,須計算雜訊溫度並轉換為折合到輸入端的雜訊功率。

雜訊溫度(Te)可以根據元件雜訊係數計算:

其中T為環境溫度(單位為K)。

根據雜訊溫度可以計算折合到輸入端的元件雜訊:

其中k為玻爾茲曼常數。

相關合併的直覺描述

訊號與雜訊合併的直覺視圖有助於理解該方法的目的。首先假設校準已執行,因此所有訊號的幅度和相位都匹配,並且雜訊不相關,但幅度也相等,合併器輸入端的所有通道都是如此。

如果僅致能了部分元件(校準或各種測試和除錯配置常常就是這種情況),那麼還需要一種方法來追蹤結果。

訊號和雜訊輸出位準可以計算如下:

訊號功率 = 輸入功率 + 訊號增益

訊號增益 = 20log(開啟的通道數)- 插入損耗 - 10log(合併器輸

入埠數)

雜訊功率 = 輸入雜訊功率 + 雜訊增益

雜訊增益 = 10log(開啟的通道數)- 插入損耗 - 10log(合併器輸

入埠數)

注意此種方法的結果。表1總結若干類比合併器通道數的訊號增益和雜訊增益,既有每個輸入都通電和校準的情況,也有僅一個輸入通電和校準而其他埠端接的情況。

表1 無損合併器的訊號/雜訊增益

|

合併通道數

|

訊號增益

(全開)

|

雜訊增益

(全開)

|

訊號增益

(單開)

|

雜訊增益

(單開)

|

|

2

|

3

|

0

|

–3

|

–3

|

|

4

|

6

|

0

|

–6

|

–6

|

|

8

|

9

|

0

|

–9

|

–9

|

級聯試算表

我們使用所描述的方法建立圖8的級聯試算表,其中包括關於追蹤已致能元件數量的規定。圖中既顯示單一元件致能的情況,也顯示八個元件致能的情況。

在資料轉換器擷取資料後,對數位資料進行快速傅立葉變換(FFT),進而得到測量結果,因此結果中包含資料轉換器規格。追蹤的最終指標是ADC指標,稱為接收器輸入。為了快速驗證測量結果,還計算了給定輸入功率的預期FFT幅度和互調產物。

(本文作者為ADI技術主管Peter Delos、應用工程師Sam Ringwood及首席電氣設計工程師Michael Jones)