數位應用與資料處理快速崛起,使得運算效能需求呈爆炸式增長。隨著擴大採用人工智慧,以面對氣候變遷、糧食短缺等重大挑戰,未來的運算需求預計會每半年翻漲一倍。為了在處理暴增的巨量資料時維持永續性,我們需要經過改良的高性能半導體技術。

為了實現這點,需要同時面對五項挑戰。雖然沒有任何企業能夠獨立完成開發,但是透過串聯半導體生態系來共同創新與合作,摩爾定律將能延續不絕:這也是比利時微電子研究中心(imec)預測半導體未來15~20年發展的要點。

半導體開發路上的五道牆

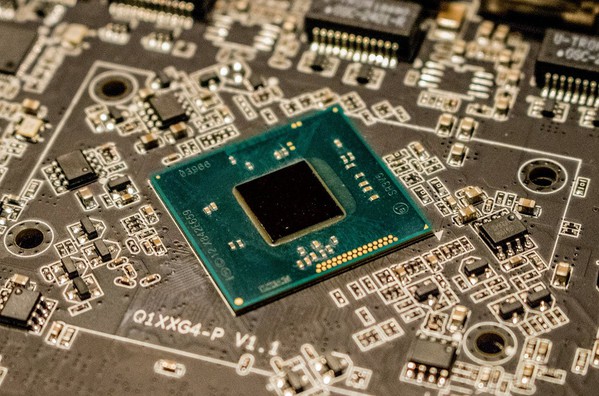

| 圖一 : 處理器與記憶體之間的傳輸路徑存在限制,導致系統效能受阻。 |

|

微縮牆(scaling wall):單純基於蝕刻製程的微縮進展逐漸趨緩。由於晶片與電晶體的結構越來越接近原子尺寸,量子效應開始干擾晶片運作,使得微縮技術難度攀高。

記憶體牆(memory wall):處理器與記憶體之間的傳輸路徑存在限制,導致系統效能受阻。實際上,記憶體頻寬趕不上處理器效能的升級速度。每秒運算次數(flop/s)大於每秒儲存容量(GB/s)。

功率牆(power wall): 晶片供電與封裝散熱越來越具挑戰性,所以我們勢必要提出改良供電與散熱的新概念。

永續力牆(sustainability wall):半導體元件製造衍生的環境足跡正在增加,包含溫室氣體與用水、自然資源及用電。

成本牆(cost wall):顯而易見,晶片製造成本可能隨著複雜度增加而暴漲,另有設計與製程開發的附帶成本。

推毀高牆

戈登.摩爾首次提出積體電路的電晶體數量會每兩年翻漲一倍,這則預言乍看之下並不符合現實。但如果我們遵循Dennard縮放定律與傳統的馮紐曼電腦架構,摩爾定律卻很可能實現。根據imec提出的微縮藍圖,未來晶片技術能夠另闢蹊徑,從根本上改良元件架構、材料、電晶體架構,以及實現典範轉移(paradigm shift)。按照imec計畫,2036年前將能從7奈米邁向2埃米,也就是0.2奈米,以每兩年或每兩年半的微縮速度循序漸進。

首先,持續開展蝕刻技術是晶片能否進一步微縮的關鍵,而傳統蝕刻是光刻,現階段所用的光波長大於圖形化所需的精度。極紫外光(EUV)光刻技術因此獲得採用。業界有越來越多的產線導入EUV技術進行量產。EUV光刻將會帶領我們從5奈米前進2奈米。

為了進一步縮小晶片,需要升級版的EUV技術:配備更大鏡面的高數值孔徑極紫外光(high-NA EUV)光刻機。這些鏡面半徑將達1公尺,精度高達20皮米。由艾司摩爾(ASML)開發的首部high-NA EUV微影機台將於2023年推出。預計將在2025年或2026年投入量產。為了降低製造風險,imec攜手ASML共同建立一套囊括所有重要構件的開發計畫,像是光罩技術、乾膜或濕膜光阻劑材料、測量技術,以及光學特性分析。

與此同時,也要在電晶體架構方面創新。目前幾乎所有晶片大廠都採用鰭式場效電晶體(FinFET)的設計。然而,邁向3奈米世代以後,FinFET受到量子干擾,造成晶片難以正常運作。

新一代架構是環繞閘極(GAA)或是由奈米片堆疊而成的奈米片電晶體,未來將能提升晶片性能,並改善短通道效應(short channel effect)。該架構將對2奈米以後的製程至關重要。三星、英特爾與台積電等全球晶片大廠皆已宣布將於3奈米與/或2奈米製程導入GAA架構。叉型片電晶體架構則出自imec設計,密度比奈米片電晶體還高,把GAA架構的概念延伸到1奈米世代。該架構在P型通道與N型通道之間導入一層阻障層,藉此縮短通道之間的距離。預計能將標準單元尺寸微縮20%。

更先進的微縮架構則是讓N型通道與P型通道相互堆疊,稱之為互補式場效電晶體(CFET),作為繼GAA架構之後的新一代垂直結構。電晶體密度因此大幅提升,但付出的代價是製程複雜度增加,尤其是針對源極與汲極的接點設計。

未來,CFET架構將納入新型的單層超薄二維材料,厚度達到原子等級,例如二硫化鎢(WS2)或是鉬(Mo)。這項晶片微縮計畫搭配光刻技術開發,將能迎向埃米世代。

2奈米以下的電晶體面臨兩大系統級的技術挑戰。記憶體頻寬沒辦法跟進處理器效能升級。記憶體資料與指令的傳輸速度是處理器運算速度的上限。為了推倒這堵「記憶體牆」,記憶體勢必要更靠近處理器。3D系統單晶片(3D SOC)整合就是備受矚目的解決方案,遠超過目前熱門的小晶片方案。

利用這套異質整合方案,晶片系統被分割成多個不同的晶片,這些晶片同時進行設計,並彼此垂直互連。如此一來,就能把靜態隨機存取記憶體(SRAM)堆疊在邏輯元件上方,作為一級快取記憶體(level-1 cache),加快記憶體與處理器之間的傳輸速度。為了實現非模組的超高頻寬效能,目前正在研發整合於光子中介層的光通訊導線(optical interconnet)。

就系統層面而言,晶片供電與散熱的技術難度逐漸增加。不過有個全新的解決方案即將出現。目前供電系統是從晶圓正面向下傳輸至電晶體,經過超過十層金屬層。imec正在開發從晶圓背面傳輸電力的技術,未來會把電源軌埋入晶圓,並選用更多元且電阻更小的材料來製成奈米矽穿孔,將這些導線連接到晶背。藉此,供電網路就會與訊號網路分離,進而提升電力傳輸系統的整體效能,減緩佈線壅塞問題,最終降低標準單元的高度。

最後一點,半導體的製造成本十分高昂。不僅用水用電量大,還會產生有害廢棄物。無論如何,整體供應鏈必須致力解決這個問題,而且需要從生態系統的角度出發。imec在去年發起了「永續半導體技術與系統(Sustainable Semiconductor Technologies and Systems)」研究計畫,整合了半導體產業價值鏈,從亞馬遜、蘋果和微軟等系統整合商,到ASM、艾司摩爾(ASML)、日本KURITA、日本SCREEN與東京電子(Tokyo Electron)等半導體設備商。最終目標是減少半導體業的總體碳足跡。這項計畫除了評估新興技術對環境的影響,也指出關鍵問題,並在技術開發的早期階段,定義更為環保的製程方案。在導入新一代技術與開發新製程前,就能先獲取充份資訊再訂定決策。

| 圖三 : 半導體的製造成本十分高昂。不僅用水用電量大,還會產生有害廢棄物,整體供應鏈必須致力解決這個問題,而且需要從生態系統的角度出發。 |

|

典範轉移

長遠來看,馮紐曼架構需要徹底改革。馮紐曼將電腦視為一個由輸入設備、中央處理單元與輸出設備組成的系統。但我們未來勢必要針對特定領域及應用來開發新一代架構,進行堪比人腦運作的大量平行運算。這代表著處理器對整體效能的影響會變小,重心會改放在滿足特定運算需求的客製化電路設計。

除了先前提到的五項技術挑戰,改革晶片架構將會開啟半導體業的歷史新章。我們需要橫跨半導體生態系,共同創新與合作,匯集晶圓代工廠、整合元件廠(IDM)、無晶圓廠、輕晶圓廠(fab lite)、設備與材料供應商。這不僅是為了延續摩爾定律,也因為半導體是高性能深度科技(deep technology)應用的關鍵,這些技術能解決當代的主要挑戰,包含氣候變遷、永續交通、空氣汙染與糧食短缺。其效益遠大於成本。

(比利時微電子研究中心(imec)是在奈米電子與數位科技領域中領先世界的研究與創新中心imec的研究技術包括先進半導體和系統微縮技術、矽光子、人工智慧、超5G通信和傳感技術,並延伸其他領域的應用,如健康與生命科學、交通運輸、工業4.0、農糧產業、智慧城市、永續能源、教育等應用領域;編譯/吳雅婷)